SmartTime Static Timing Analyzer User Guide

113

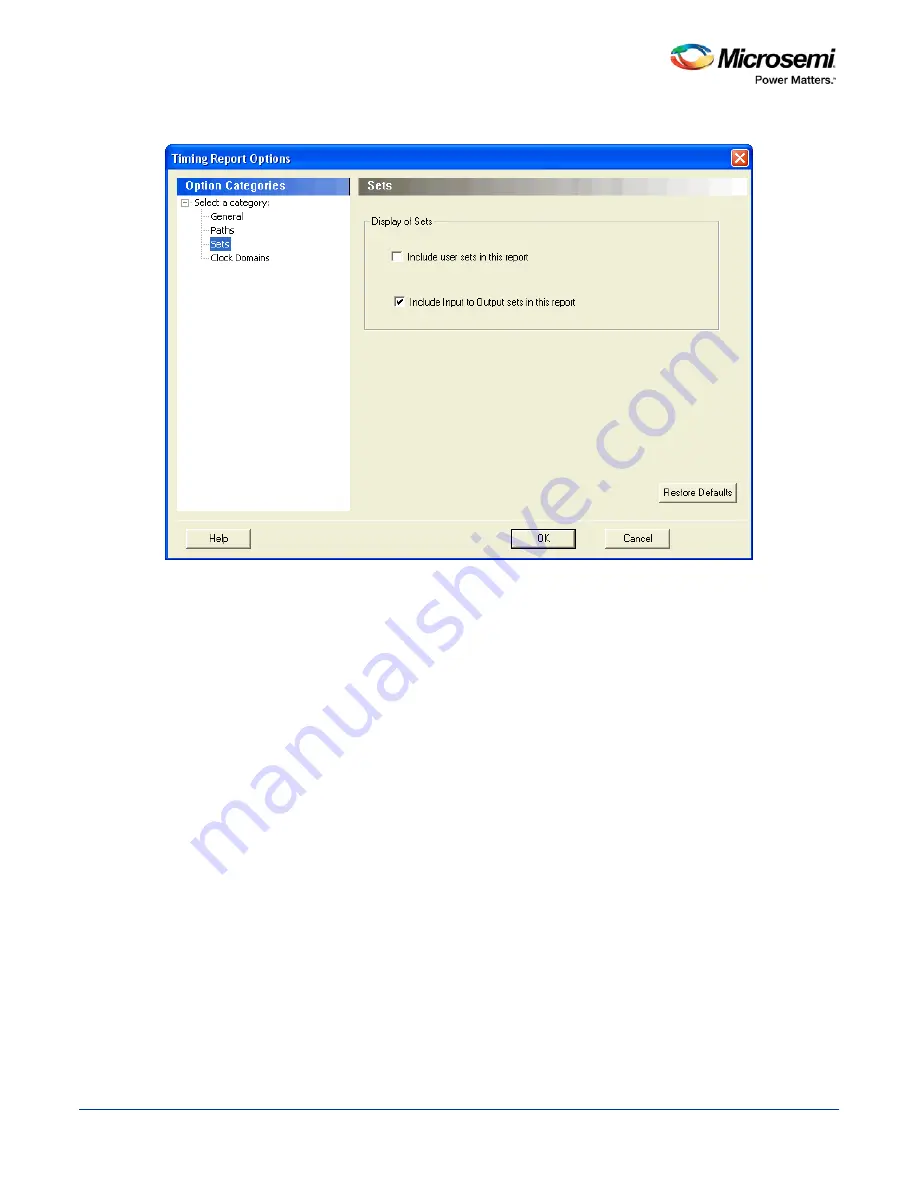

Sets

Figure 91 · Timing Report Options - Sets Dialog Box

Display of Sets

Specifies whether or not the user sets will be included in the timing report.

User sets are either filters that you have created and stored on the default paths sets (Register to Register,

Inputs to Register, etc.) or Pin to Pin user sets. By default, the paths for these sets are not reported.

In addition, specify whether the Inputs to Output sets will be included in the report. By default, the Input to

Output sets are reported.

Restore Defaults

Resets both options in the Sets panel to their default values.

Содержание SmartTime

Страница 2: ......

Страница 6: ......

Страница 15: ...SmartTime Static Timing Analyzer User Guide 15 SmartTime Timing Analyzer ...

Страница 31: ...SmartTime Static Timing Analyzer User Guide 31 Advanced Timing Analysis ...

Страница 37: ...SmartTime Static Timing Analyzer User Guide 37 Generating Timing Reports ...

Страница 57: ...SmartTime Static Timing Analyzer User Guide 57 Timing Concepts ...

Страница 66: ...SmartTime Static Timing Analyzer User Guide 66 ...

Страница 91: ...SmartTime Static Timing Analyzer User Guide 91 Q_reg NOT2 end not u1 NOT1 MUX2 not u2 NOT2 NOT1 endmodule ...

Страница 92: ...SmartTime Static Timing Analyzer User Guide 92 Dialog Boxes ...

Страница 118: ...SmartTime Static Timing Analyzer User Guide 118 Tcl Commands ...