SmartTime Static Timing Analyzer User Guide

83

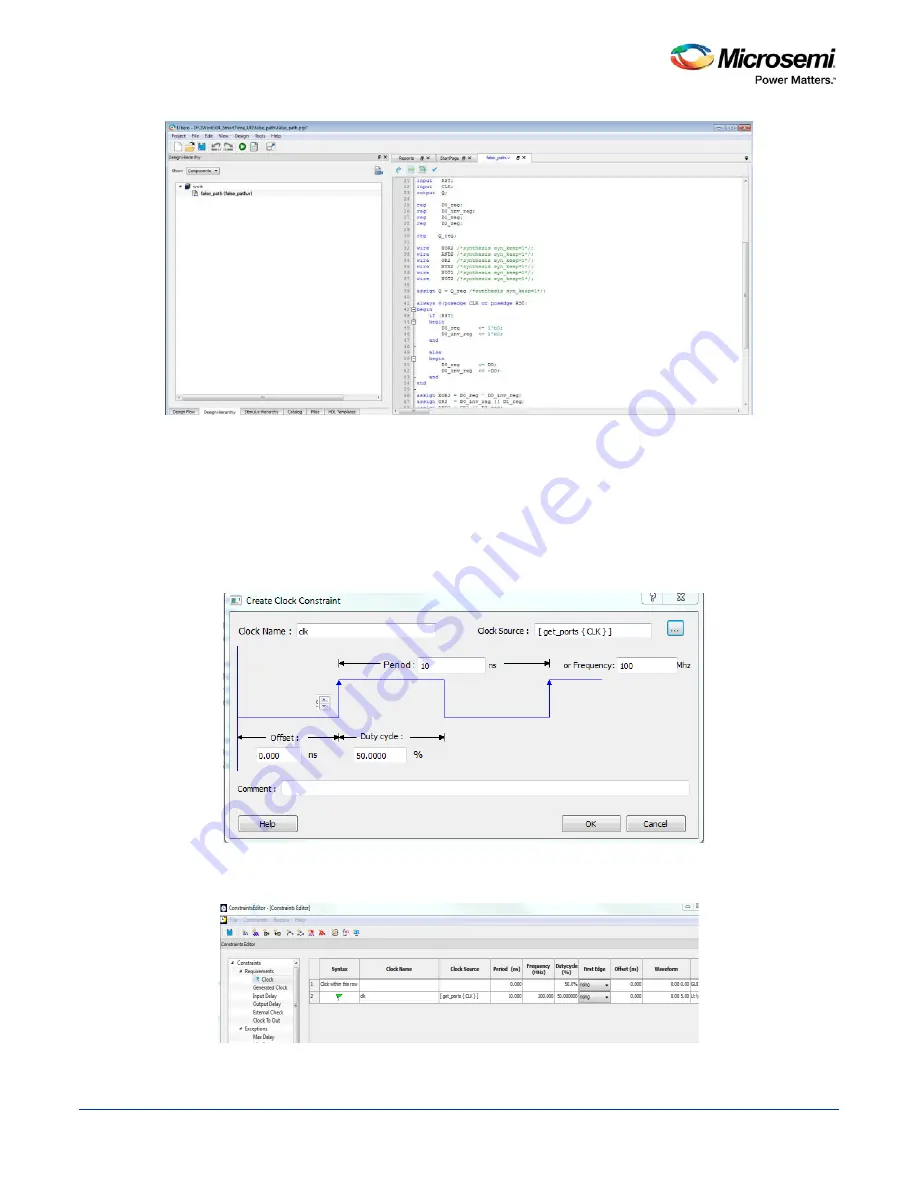

Figure 61 · false_path Design in Design Hierarchy

4. In the Design Flow window, double-click

Synthesize

to run synthesis. A green check mark appears

when the Synthesis step completes successfully.

5. Expand

Edit Constraints

. Right-click

Timing Constraints

and choose

Open Interactivel

y.

6. Double-click on

Manage Constraints

. Select the Timing tab, pull down the

Edit with Constraint

Editor

sub-menu, and select the "Edit Place and Route Constraints". The Constraints Editor will open.

7. Double-click on the

Requirements

:

Clock

and the

Create Clock Constraint

dialog box will open.

8. Double click the browse button for Clock Source, and select CLK; name it clk (or whatever you want).

9. Set the frequency to be 100 MHz.

Figure 62 · Create 100 MHz clock

10. Click OK to return to the Constraints Editor and observe that the clock information has been filled in as

shown in the figure below.

Figure 63 · Clock Constraint of 100 MHz in false_path design

Содержание SmartTime

Страница 2: ......

Страница 6: ......

Страница 15: ...SmartTime Static Timing Analyzer User Guide 15 SmartTime Timing Analyzer ...

Страница 31: ...SmartTime Static Timing Analyzer User Guide 31 Advanced Timing Analysis ...

Страница 37: ...SmartTime Static Timing Analyzer User Guide 37 Generating Timing Reports ...

Страница 57: ...SmartTime Static Timing Analyzer User Guide 57 Timing Concepts ...

Страница 66: ...SmartTime Static Timing Analyzer User Guide 66 ...

Страница 91: ...SmartTime Static Timing Analyzer User Guide 91 Q_reg NOT2 end not u1 NOT1 MUX2 not u2 NOT2 NOT1 endmodule ...

Страница 92: ...SmartTime Static Timing Analyzer User Guide 92 Dialog Boxes ...

Страница 118: ...SmartTime Static Timing Analyzer User Guide 118 Tcl Commands ...