MB89620 series

CHAPTER 3 CPU

83

n

External Bus Connection Example

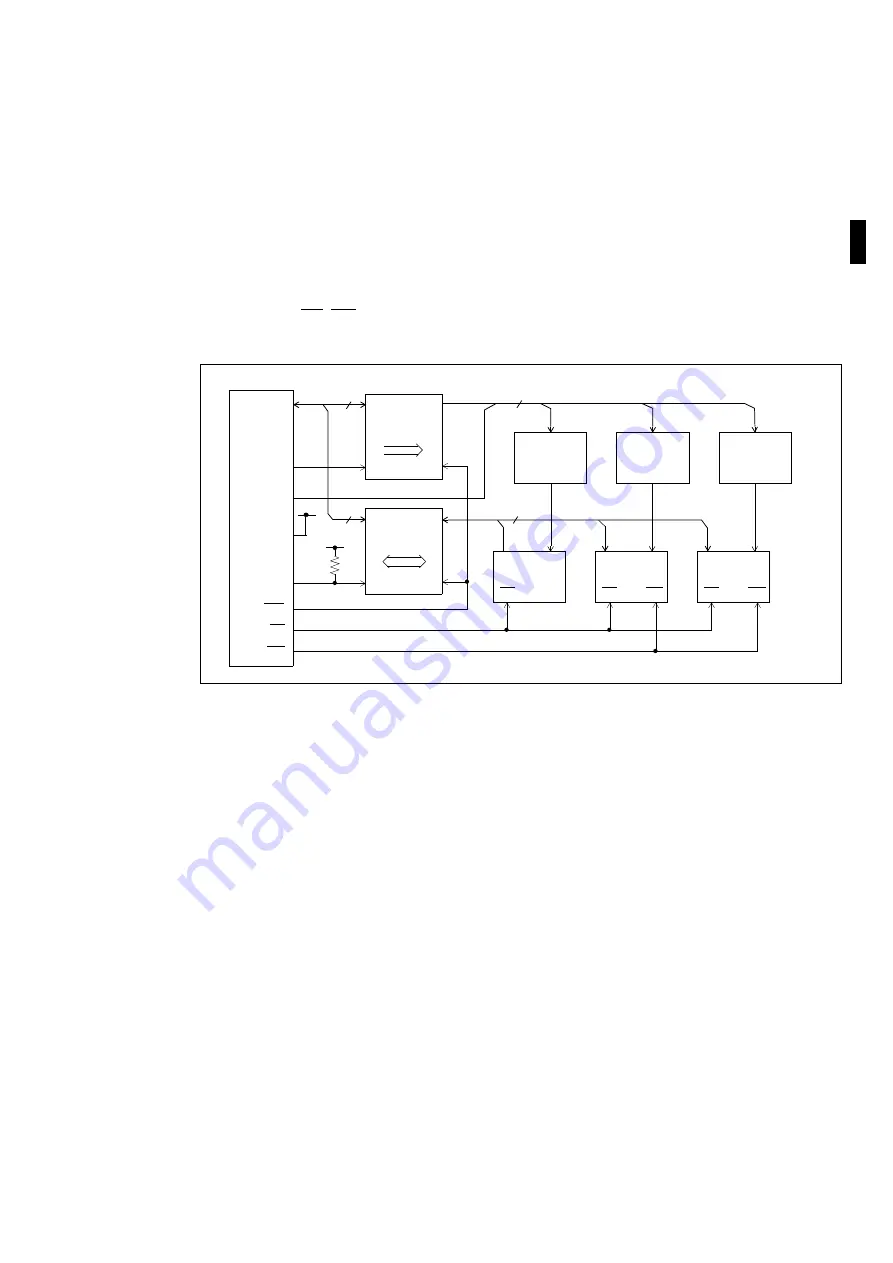

This section gives an example of connecting external memory and a peripheral function in

external bus operation. The connection example shows the external bus is used after hold

operation of the external bus pin control register (BCTR: HLD=“1”) is enabled in internal ROM/

external bus mode. An external pull-up resistor must be connected to the BUFC pin when using

the hold function. Also, the AD0 to AD7, A08 to A15, and ALE signals are output during internal

access but the RD, WR, and BUFC pins output an “H” level.

Figure 3.8.4b shows the example of connecting external memory and a peripheral function.

Figure 3.8.4b Example of Connecting External Memory and Peripheral Function

D

Q

G

OC

A

B

DIR

G

Address

decoder

Address

decoder

Address

decoder

D

CS

RD

ROM

D

CS

RD

WR

RAM

D

CS

RD

WR

Peripheral function

AD0 to AD7

ALE

A08 to A15

BUFC

HAK

RD

WR

8

8

8

16

A0 to A15

D0 to D7

MB89620 series

Address

latch

Data bus

buffer

RDY

Содержание F2MC-8L MB89620 Series

Страница 8: ......

Страница 10: ...MB89620 series ...

Страница 11: ...vi MB89620 series ...

Страница 17: ...xii MB89620 series ...

Страница 18: ...xvi MB89620 series ...

Страница 30: ...MB89620 series CHAPTER 1 OVERVIEW 9 Memo ...

Страница 34: ...MB89620 series CHAPTER 1 OVERVIEW 13 Memo ...

Страница 42: ...MB89620 series CHAPTER 1 OVERVIEW 21 Memo ...

Страница 49: ...28 CHAPTER 1 OVERVIEW MB89620 series ...

Страница 62: ...MB89620 series CHAPTER 3 CPU 41 Memo ...

Страница 78: ...MB89620 series CHAPTER 3 CPU 57 Memo ...

Страница 82: ...MB89620 series CHAPTER 3 CPU 61 Memo ...

Страница 86: ...MB89620 series CHAPTER 3 CPU 65 Memo ...

Страница 90: ...MB89620 series CHAPTER 3 CPU 69 Memo ...

Страница 96: ...MB89620 series CHAPTER 3 CPU 75 Memo ...

Страница 122: ...MB89620 series CHAPTER 4 I O PORTS 101 Memo ...

Страница 144: ...MB89620 series CHAPTER 5 TIMEBASE TIMER 123 Memo ...

Страница 149: ...128 CHAPTER 5 TIMEBASE TIMER MB89620 series ...

Страница 157: ...136 CHAPTER 6 WATCHDOG TIMER MB89620 series ...

Страница 174: ...MB89620 series CHAPTER 7 8 BIT PWM TIMER 153 Memo ...

Страница 177: ...156 CHAPTER 7 8 BIT PWM TIMER MB89620 series ...

Страница 202: ...MB89620 series CHAPTER 9 16 BIT TIMER COUNTER 181 Memo ...

Страница 217: ...196 CHAPTER 9 16 BIT TIMER COUNTER MB89620 series ...

Страница 220: ...MB89620 series CHAPTER 10 8 BIT SERIAL I O SERIAL I O 1 AND SERIAL I O 2 199 Memo ...

Страница 228: ...MB89620 series CHAPTER 10 8 BIT SERIAL I O SERIAL I O 1 AND SERIAL I O 2 207 Memo ...

Страница 245: ...224 CHAPTER 10 8 BIT SERIAL I O SERIAL I O 1 AND SERIAL I O 2 MB89620 series ...

Страница 266: ...MB89620 series CHAPTER 13 A D CONVERTER 245 13 Memo ...

Страница 283: ...262 CHAPTER 13 A D CONVERTER MB89620 series ...

Страница 289: ...268 CHAPTER 14 CLOCK MONITOR FUNCTION MB89620 series ...

Страница 306: ...MB89620 series APPENDIX 285 APPEND Memo ...

Страница 319: ...298 APPENDIX MB89620 series Memo ...

Страница 321: ...2 ...

Страница 354: ......