xr

PRELIMINARY

XRT86VL38

REV. P1.0.6

OCTAL T1/E1/J1 FRAMER/LIU COMBO

242

1

RXAINT

RUR/WC

0

Change in Receive Loopback Activation Code interrupt Status

This Reset-Upon-Read bit field indicates whether or not the

“Change in Receive Loopback Activation Code” interrupt has

occurred since the last read of this register.

If this interrupt is enabled, then the Receive T1/E1 Framer block will

generate an interrupt in response to either one of the following

conditions.

1.

Whenever the Receive T1/E1 Framer block detects the

Receive Loopback Activation Code.

2.

Whenever the Receive T1/E1 Framer block no longer detects

the Receive Loopback Activation Code.

0 = Indicates that the “Change in Receive Loopback Activation

Code” interrupt has not occurred since the last read of this register

1 = Indicates that the “Change in Receive Loopback Activation

Code” interrupt has occurred since the last read of this register

0

RXDINT

RUR/WC

0

Change in Receive Loopback Deactivation Code interrupt Sta-

tus

This Reset-Upon-Read bit field indicates whether or not the

“Change in Receive Loopback Deactivation Code” interrupt has

occurred since the last read of this register.

If this interrupt is enabled, then the Receive T1/E1 Framer block will

generate an interrupt in response to either one of the following

conditions.

1.

Whenever the Receive T1/E1 Framer block detects the

Receive Loopback Deactivation Code.

2.

Whenever the Receive T1/E1 Framer block no longer detects

the Receive Loopback Deactivation Code.

0 = Indicates that the “Change in Receive Loopback Deactivation

Code” interrupt has not occurred since the last read of this register

1 = Indicates that the “Change in Receive Loopback Deactivation

Code” interrupt has occurred since the last read of this register

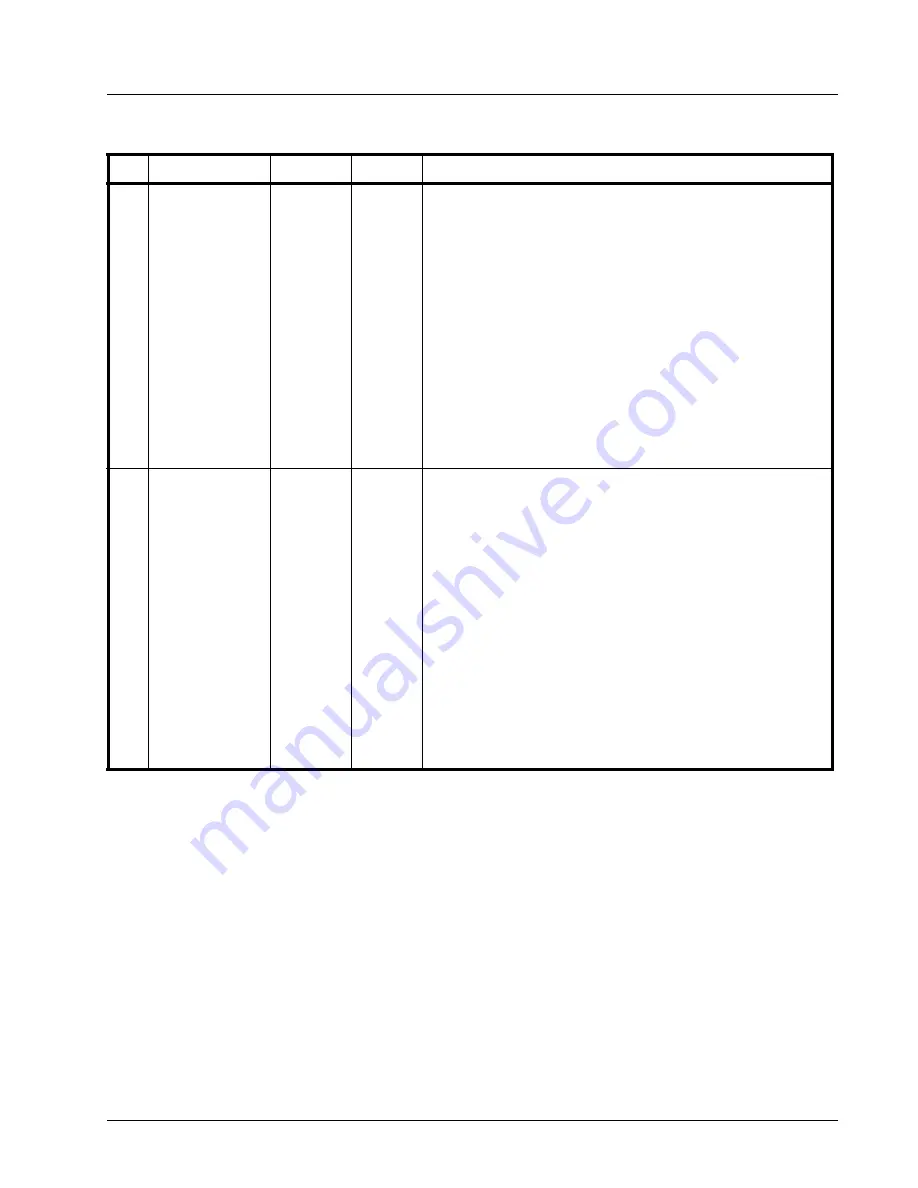

T

ABLE

137: R

ECEIVE

L

OOPBACK

C

ODE

I

NTERRUPT

AND

S

TATUS

R

EGISTER

(RLCISR)

R

EGISTER

537 R

ECEIVE

L

OOPBACK

C

ODE

I

NTERRUPT

AND

S

TATUS

R

EGISTER

(RLCISR) H

EX

A

DDRESS

: 0

X

nB0A

B

IT

F

UNCTION

T

YPE

D

EFAULT

D

ESCRIPTION

-O

PERATION