ML610Q111/ML610Q112 User’s Manual

Chapter 12 UART

FEUL610Q111

12-16

12.3.4

Transmit Operation

Transmission is started by setting the UnIO bit of the UARTn mode register 0 (UA0MOD0) to “0” to select transmit mode

and setting the UnEN bit of the UARTn control register (UAnCON) to “1”.

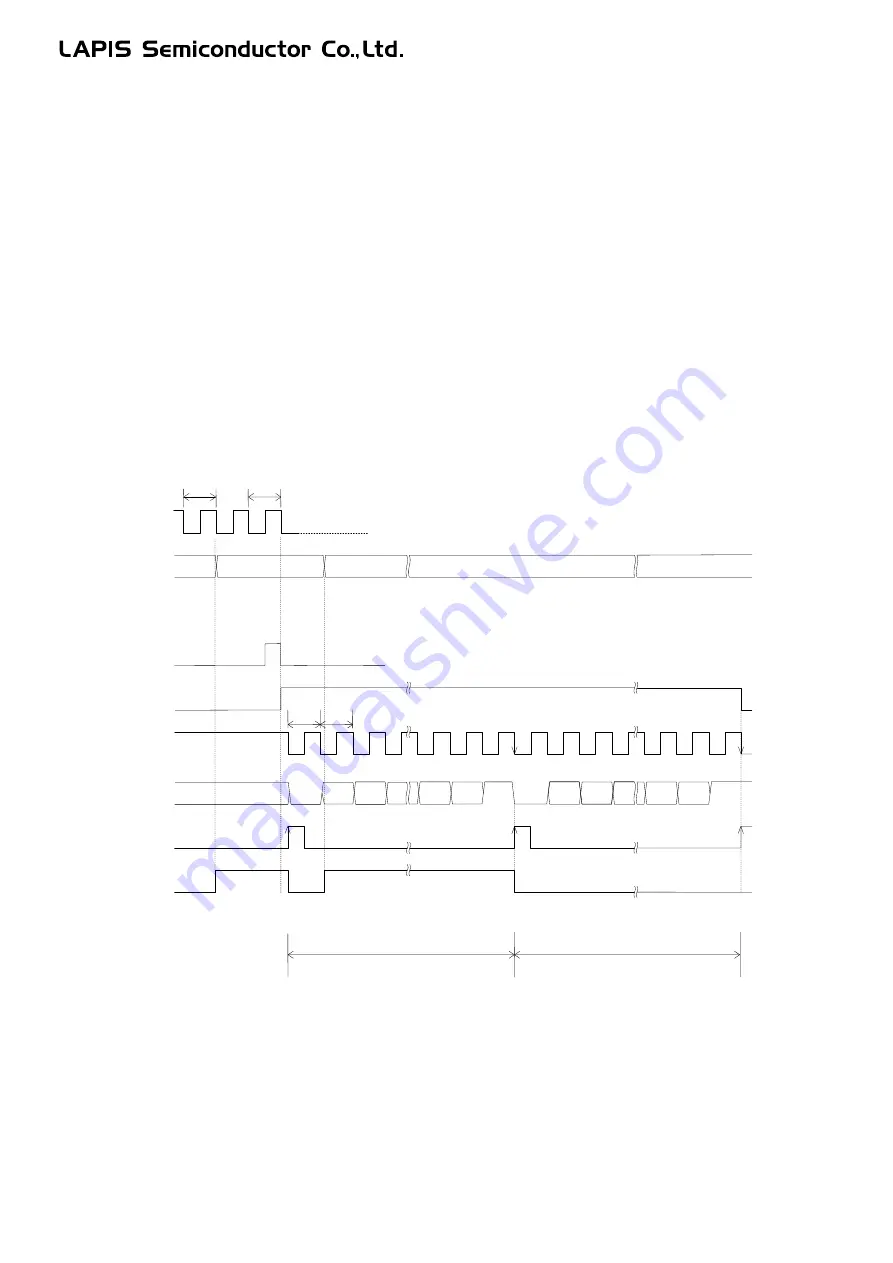

Figure 12-5 shows the operation timing for transmission.

When the UnEN bit is set to “1” (

), the baud rate generator generates an internal transfer clock of the baud rate set and

starts transmission.

The start bit is output to the TXDn pin by the falling edge of the internal transfer clock (

). Subsequently, the transmitted

data, a parity bit, and a stop bit are output.

When the start bit is output (

), a UARTn interrupt is requested. In the UARTn interrupt routine, the next data to be

transmitted is written to the transmit/receive buffer (UAnBUF).

When the next data to be transmitted is written to the transmit/receive buffer (UAnBUF), the transmit buffer status flag

(UnFUL) is set to “1” (

) and a UARTn interrupt is requested on the falling edge of the internal transfer clock (

) after

transmission of the stop bit. If the UARTn interrupt routine is terminated without writing the next data to the

transmit/receive buffer, the UnFUL bit is not set to “1” (

) and transmission continues up to the transmission of the stop

bit, then the UnEN bit is reset to “0” and a UARTn interrupt is requested.

The valid period for the next transmit data to be written to the transmit/receive buffer is from the generation of an interrupt

to the termination of stop bit transmission. (

)

Figure 12-5 Operation Timing in Transmission

2nd data

1st data

Transmit/receive buffer

write enable period

UAnBUF write

instruction

UnEN set

instruction

SYSCLK

UAnBUF

UnEN

TXDn output

UAnINT

UnFUL

BRT

BRT

Start

0

1

2

7

Parity

Stop

Start

0

1

2

7

Parity

Stop

Transmit/receive buffer write

enable period

Internal

transfer clock

UnEN

setting signal

Summary of Contents for ML610Q111

Page 1: ...ML610Q111 ML610Q112 User s Manual Issue Date Nov 16 2016 FEUL610Q111 05 ...

Page 14: ...Chapter 1 Overview ...

Page 26: ...Chapter 2 CPU and Memory Space ...

Page 34: ...Chapter 3 Reset Function ...

Page 38: ...Chapter 4 MCU Control Function ...

Page 53: ...Chapter 5 Interrupts INTs ...

Page 81: ...Chapter 6 Clock Generation Circuit ...

Page 95: ...Chapter 7 Time Base Counter ...

Page 103: ...Chapter 8 Timers ...

Page 145: ...Chapter 9 Watchdog Timer ...

Page 153: ...Chapter 10 PWM ...

Page 199: ...Chapter 11 Synchronous Serial Port ...

Page 212: ...Chapter 12 UART ...

Page 240: ...Chapter 13 I2 C Bus Interface Master ...

Page 254: ...Chapter 14 I2 C Bus Interface Slave ...

Page 269: ...Chapter 15 Port A ...

Page 279: ...Chapter 16 Port B ...

Page 291: ...Chapter 17 Port C ...

Page 303: ...Chapter 18 Port D ...

Page 312: ...Chapter 19 Port AB Interrupts ...

Page 317: ...Chapter 20 Successive Approximation Type A D Converter ...

Page 335: ...Chapter 21 Voltage Level Supervisor ...

Page 342: ...Chapter 22 Analog Comparator ...

Page 353: ...Chapter 23 Data Flash Memory ...

Page 373: ...Chapter 24 On chip Debug ...

Page 375: ...Appendixes ...

Page 393: ...Appendix E ...

Page 398: ...Revision History ...