Rev. 1.00

460 of 486

July 31, 2018

32-Bit Arm

®

Cortex

®

-M0+ MCU

HT32F50231/HT32F50241

21 Universal Synchronous

Asynchronous Receiver T

ransmitter (USART)

21 Universal Synchronous

Asynchronous Receiver T

ransmitter (USART)

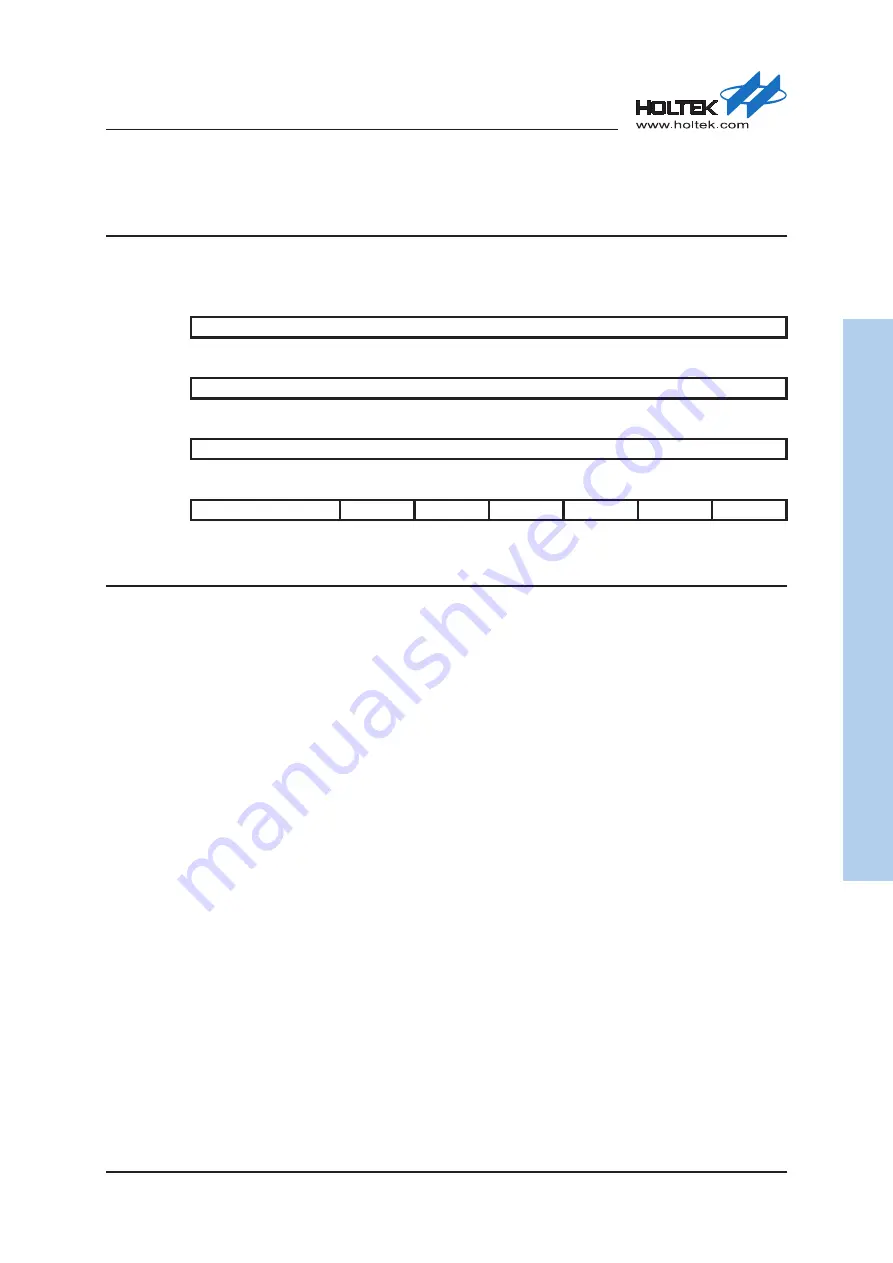

USART IrDA Control Register – IrDACR

This register is used to control the IrDA mode of USART.

Offset:

0x018

Reset value: 0x0000_0000

31

30

29

28

27

26

25

24

Reserved

Type/Reset

23

22

21

20

19

18

17

16

Reserved

Type/Reset

15

14

13

12

11

10

9

8

IrDAPSC

Type/Reset RW 0 RW 0 RW 0 RW 0 RW 0 RW 0 RW 0 RW 0

7

6

5

4

3

2

1

0

Reserved

RXINV

TXINV

LB

TXSEL

IrDALP

IrDAEN

Type/Reset

RW 0 RW 0 RW 0 RW 0 RW 0 RW 0

Bits

Field

Descriptions

[15:8]

IrDAPSC

IrDA Prescaler value

This field contains the 8-bit debounce prescaler value.

The debounce count-down counter is driven by the USART clock, named as CK_

USART. The counting period is specified by the IrDAPSC field. The IrDAPSC field

must be set to a value equal to or greater than 0x01 for normal debounce counter

operation. If the pulse width is less than the duration specified by the IrDAPSC field,

the pulse will be considered as glitch noise and discarded.

00000000: Reserved – can not be used.

00000001: CK_USART clock divided by 1

00000010: CK_USART clock divided by 2

00000011: CK_USART clock divided by 3

...

[5]

RXINV

RX Signal Inverse Control

0: No inversion

1: RX input signal is inversed

[4]

TXINV

TX Signal Inverse Control

0: No inversion

1: TX output signal is inversed

[3]

LB

IrDA Loop Back Mode

0: Disable IrDA loop back mode

1: Enable IrDA loop back mode for self-testing

[2]

TXSEL

Transmit Select

0: Enable IrDA receiver

1: Enable IrDA transmitter

[1]

IrDALP

IrDA Low Power Mode

Select the IrDA operation mode.

0: Normal mode

1: IrDA low power mode