Rev. 1.00

416 of 486

July 31, 2018

32-Bit Arm

®

Cortex

®

-M0+ MCU

HT32F50231/HT32F50241

19 Inter-Integrated Circuit (I2C)

19 Inter-Integrated Circuit (I2C)

I

2

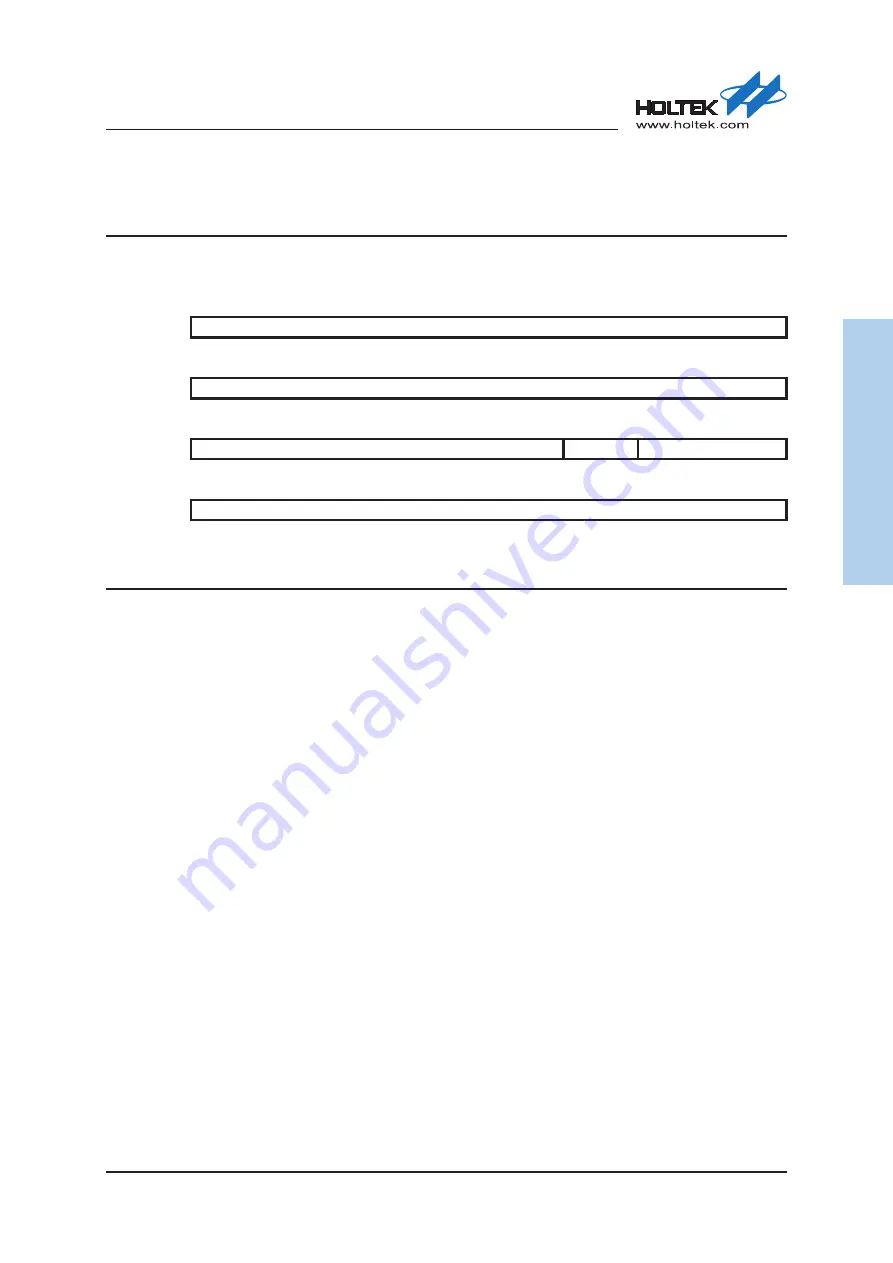

C Target Register – I2CTAR

This register specifies the target device address to be communicated.

Offset:

0x01C

Reset value: 0x0000_0000

31

30

29

28

27

26

25

24

Reserved

Type/Reset

23

22

21

20

19

18

17

16

Reserved

Type/Reset

15

14

13

12

11

10

9

8

Reserved

RWD

TAR

Type/Reset

RW 0 RW 0 RW 0

7

6

5

4

3

2

1

0

TAR

Type/Reset RW 0 RW 0 RW 0 RW 0 RW 0 RW 0 RW 0 RW 0

Bits

Field

Descriptions

[10]

RWD

Read or Write Direction

0: Write direction to target slave address

1: Read direction from target slave address

If this bit is set to 1 in the 10-bit master receiver mode, the I

2

C interface will initiate

a byte with a value of 11110XX0b in the first header frame and then continue to

deliver a byte with a value of 11110XX1b in the second header frame by hardware

automatically.

[9:0]

TAR

Target Slave Address

The I

2

C interface will assign a START signal and send a target slave address

automatically once the data is written to this register. When the system wants to

send a repeated START signal to the I

2

C bus, the timing is suggested to set the

I2CTAR register after a byte transfer is completed. It is not allowed to set TAR in the

address frame. I2CTAR[9:7] is not available under the 7-bit addressing mode.