UG-1262

Rev. B | Page 87 of 312

16

67

5-

01

7

+

PA

–

SW2

SW13

+

LPTIA

–

SW7

10kΩ

SW3

SW4

SW10

SW8

SW15

RE1

SW6

SW1

SW5

SW0

SW11

R

LOAD

LPTIACON1

[9:5]

LPTIACON1

[12:10]

CE1

CAP_POT1

RE1

SE1

RC1_0

RC1_1

SE0

TSWFULLCON[4]

T5

TSWFULLCON[6]

T7

SE1

VBIAS1

LPDACSW1[3]

OPEN: LPDACCON1[5] = 1

AND LPDACSW1[4] = 0

LPDACCON1[3]

LPDACCON1[4]

VZERO1

VREF_2.5V

AIN7_LPF1

FORCE/SENSE

R

LPF

LPTIACON1

[15:13]

SW9

10kΩ

R

TIA

LPDAC1

12-BIT

6-BIT

LPBUF

LPREF

SW12

LPDACSW1[1]

ADC

MUX

VZERO1

HSTIA

ADCVBIAS_CAP (1.11V)

LPDACSW1[0]

VZERO1

VZERO0

LPDACSW0[0]

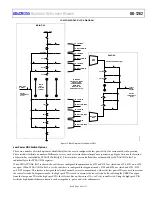

Figure 17. Low Power TIA, Low Power Potentiostat, and Low Power DAC Switches for Channel 1

1.6kΩ

3.1kΩ

3.6kΩ

10Ω

0Ω

10Ω

30Ω

50Ω

100Ω

20Ω

20Ω

50Ω

110Ω

890Ω

110Ω

(POT)

1kΩ

2kΩ

3kΩ

4kΩ

6kΩ

500Ω

2kΩ

500Ω

500Ω

1kΩ

500Ω

166

75-

259

Figure 18. Low Power TIA R

LOAD

and R

GAIN

Configuration