PMBUS Communications Fault Handling

382

SNIU028A – February 2016 – Revised April 2016

Copyright © 2016, Texas Instruments Incorporated

PMBus Interface/I2C Interface

10.8.2 Test Mode (Manufacturer Reserved Address Match)

If a PMBus message to the UCD accesses the reserved address of 0x7f, the UCD may begin a test mode

entry sequence. It may hold the data line low. In this case, additional transitions on the PMBus clock line

will return the PMBus to normal functionality. On the UCD3138128/A64 and the A versions of the same

device, the test mode entry address is 0x7e. This is less likely to occur as a fault case.

10.9 Other Functions of the PMBus Module

There are other functions available in the PMBus module. The 4 PMBus pins can be used as general

purpose I/O. This can be done using the GLOBAL IO registers in the Miscellaneous Analog memory

space. It can also be done using the PMBCTRL3 register for configuration and the PMBST register for

monitoring. All of these bits follow standard microprocessor peripheral protocol, so no further description is

necessary beyond the reference section above.

The PMBCTRL3 register also has 2 bits called IBIAS_A_EN and IBIAS_B_EN. These bits are used to

enable a small current onto 2 ADC pins to permit the use of resistors on those pins for setting the PMBus

address. See

for more information.

10.10 PMBus Interface Registers Reference

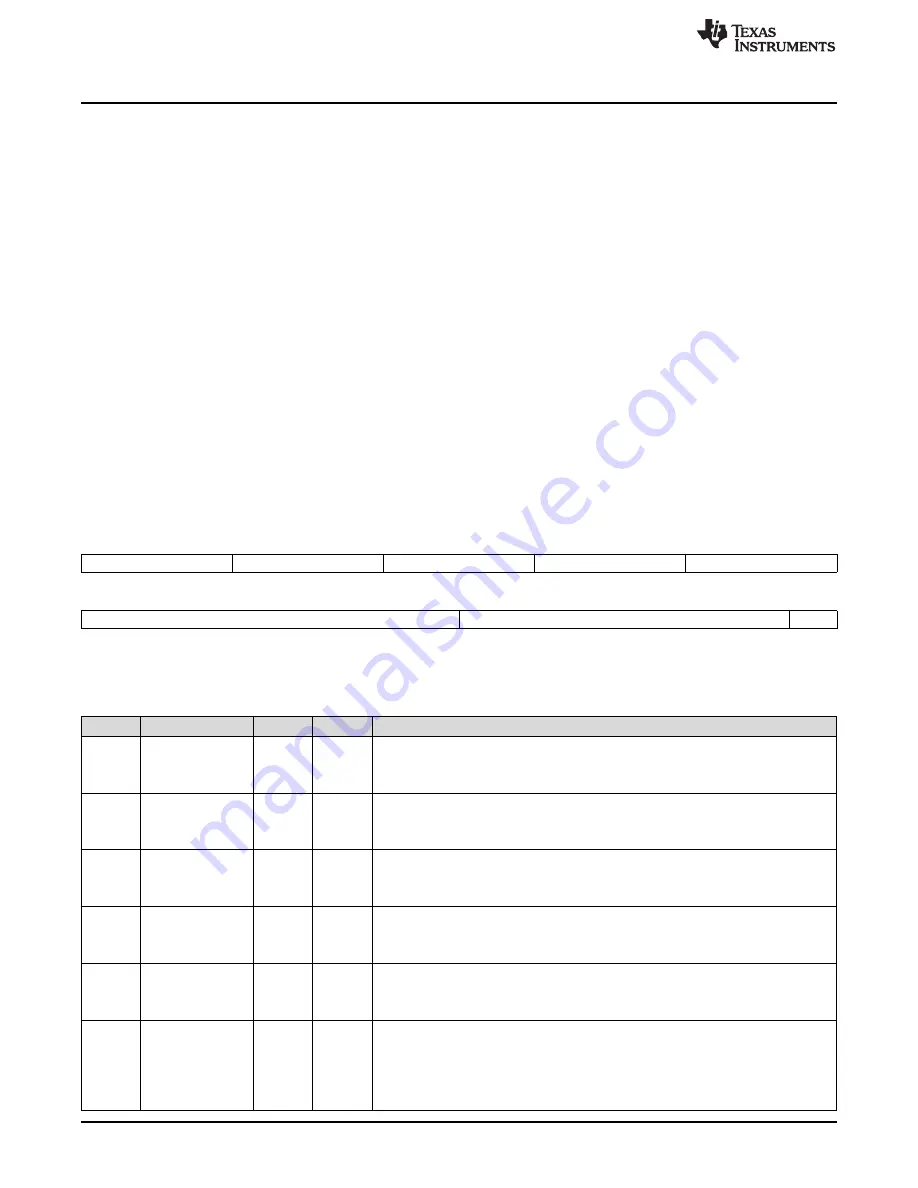

10.10.1 PMBUS Control Register 1 (PMBCTRL1)

Address FFF7F600

Figure 10-53. PMBUS Control Register 1 (PMBCTRL1)

20

19

18

17

16

PRC_CALL

GRP_CMD

PEC_ENA

EXT_CMD

CMD_ENA

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

BYTE_COUNT

SLAVE_ADDR

RW

R/W-0000 0000

R/W-000 0000

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -

n

= value after reset

Table 10-5. PMBUS Control Register 1 (PMBCTRL1) Register Field Descriptions

Bit

Field

Type

Reset

Description

20

PRC_CALL

R/W

0

Master Process Call Message Enable

0 = Default state for all messages besides Process Call message (Default)

1 = Enables transmission of Process Call message

19

GRP_CMD

R/W

0

Master Group Command Message Enable

0 = Default state for all messages besides Group Command message (Default)

1 = Enables transmission of Group Command message

18

PEC_ENA

R/W

0

Master PEC Processing Enable

0 = Disables PEC processing (Default)

1 = Enables PEC byte transmission/reception

17

EXT_CMD

R/W

0

Master Extended Command Code Enable

0 = Use 1 byte for Command Code (Default)

1 = Use 2 bytes for Command Code

16

CMD_ENA

R/W

0

Master Command Code Enable

0 = Disables use of command code on Master initiated messages (Default)

1 = Enables use of command code on Master initiated messages

15-8

BYTE_COUNT

R/W

0000

0000

Indicates number of data bytes transmitted in current message. Byte count does not

include any device addresses, command words or block lengths in block messages.

In block messages, the PMBus Interface automatically inserts the block length into

the message based on the byte count setting. The firmware only needs to load the

address, command words and data to be transmitted. PMBus Interface supports byte

writes up to 255 bytes.