Filter Registers Reference

158

SNIU028A – February 2016 – Revised April 2016

Copyright © 2016, Texas Instruments Incorporated

Filter

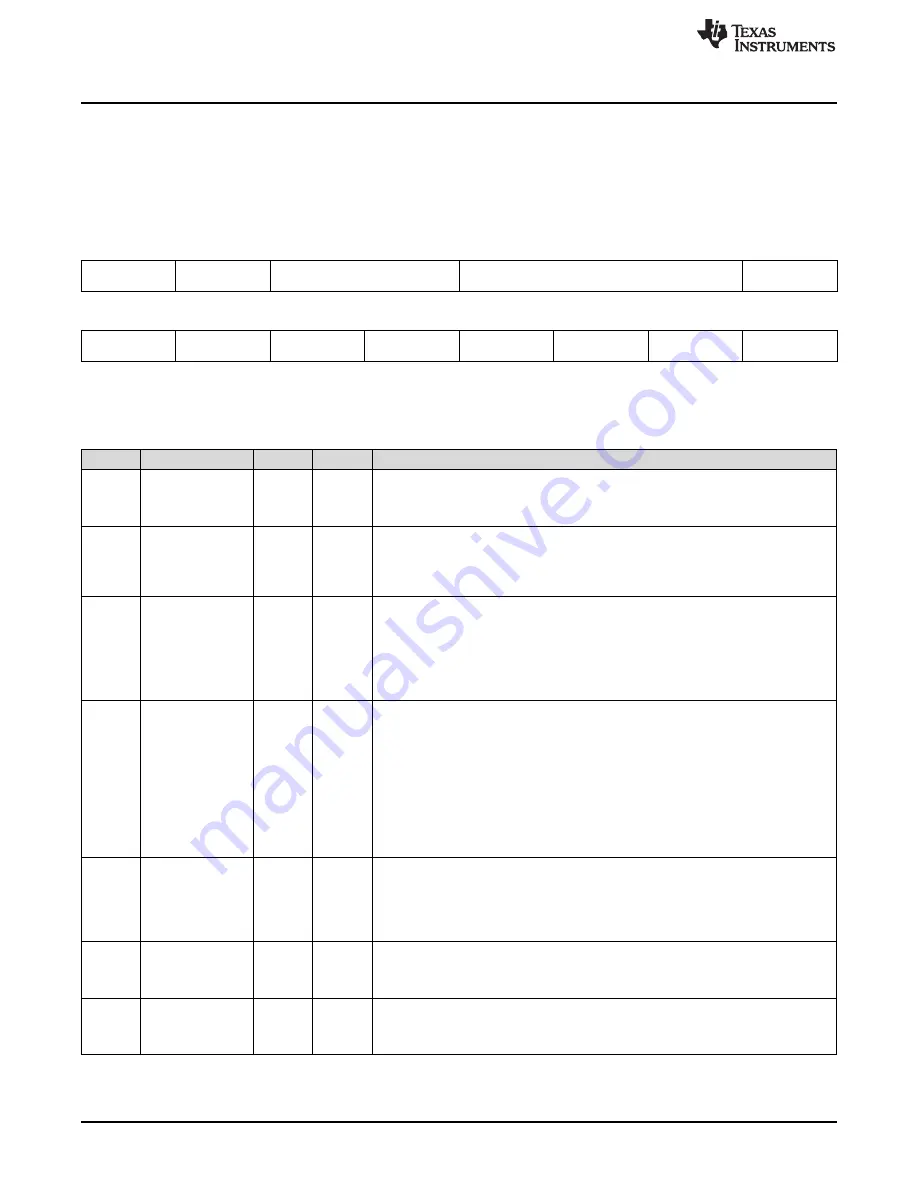

4.11.2 Filter Control Register (FILTERCTRL)

Address 00060004 – Filter 2 Control Register

Address 00090004 – Filter 1 Control Register

Address 000C0004 – Filter 0 Control Register

Figure 4-7. Filter Control Register (FILTERCTRL)

15

14

13

12

11

9

8

KI_ADDER

_MODE

PERIOD_MULT

_SEL

OUTPUT_MULT_SEL

YN_SCALE

NL_MODE

R/W-1

R/W-0

R/W-00

R/W-000

R/W-0

7

6

5

4

3

2

1

0

KD_STALL

KI_STALL

KP_OFF

KD_OFF

KI_OFF

FORCE_

START

USE_CPU_

SAMPLE

FILTER_EN

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-0

R/W-1

LEGEND: R/W = Read/Write; R = Read only; -

n

= value after reset

Table 4-2. Filter Control Register (FILTERCTRL) Register Field Descriptions

Bit

Field

Type

Reset

Description

15

KI_ADDER_MODE R/W

1

Configures addition of Xn and Xn-1 in Integral branch

0 = Only Xn used for addition (Xn + 0)

1 = Xn + Xn-1 used for addition (Default)

14

PERIOD_MULT

_SEL

R/W

0

Selects output multiplicand used for multiplying with filter output to calculate DPWM

Period value in Resonant Mode

0 = Switching period received from Loop Mux module (Default)

1 = KComp received from Loop Mux module

13-12

OUTPUT_MULT

_SEL

R/W

00

Selects output multiplicand used for multiplying with filter output to calculate DPWM

Duty value

0 = KComp received from Loop Mux module (Default)

1 = Switching period received from Loop Mux module

2 = Feed-Forward value received from Loop Mux module

3 = Resonant Duty value received from DPWM Module

11-9

YN_SCALE

R/W

000

Controls scaling of Yn value to compensate for filter coefficient scaling

-4 = Filter output (Yn) left shifted by 4

-3 = Filter output (Yn) left shifted by 3

-2 = Filter output (Yn) left shifted by 2

-1 = Filter output (Yn) left shifted by 1

0 = Filter output (Yn) not scaled (Default)

1 = Filter output (Yn) right shifted by 1

2 = Filter output (Yn) right shifted by 2

3 = Filter output (Yn) right shifted by 3

8

NL_MODE

R/W

0

Sets non-linear gain table configuration. Coefficient Bin mapping is controlled by

Coefficient Configuration Register. Limit configuration is controlled by the Filter

Nonlinear Limit Registers (See

0 = Non-symmetric mode (Default)

1 = Symmetric mode

7

KD_STALL

R/W

0

Freezes KD Branch, KD_YN remains at current value

0 = KD_YN recalculated on each filter update (Default)

1 = KD_YN stalled at present value

6

KI_STALL

R/W

0

Freezes KI Branch, KI_YN remains at current value

0 = KI_YN recalculated on each filter update (Default)

1 = KI_YN stalled at present value