Data Transmission and Reception

11-25

Multichannel Buffered Serial Ports

In a system where the same clock (internal or external) is used to clock the re-

ceiver and transmitter, CLKRP = CLKXP. The receiver uses the opposite edge

as the transmitter to ensure valid setup and hold times of data around this edge.

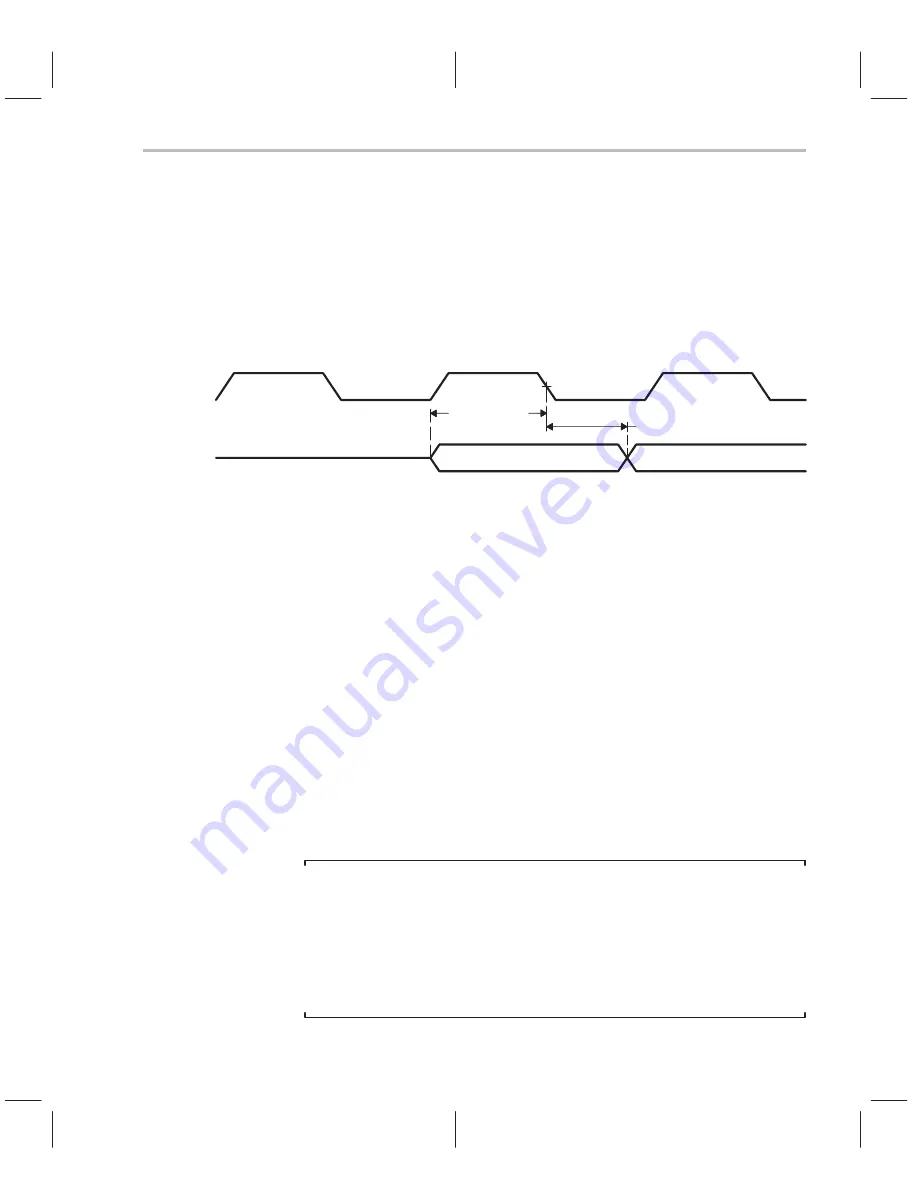

Figure 11–7 shows how data clocked by an external serial device using a rising-

edge clock can be sampled by the McBSP receiver with the falling edge of the

same clock.

Figure 11–7.Receive Data Clocking

DR

CLKR_int

B6

B7

Data hold

Data setup

ÁÁÁÁÁÁÁÁ

ÁÁ

ÁÁ

11.3.4.2 Frame Synchronization Phases

Frame synchronization indicates the beginning of a transfer on the McBSP.

The data stream following frame synchronization can have up to two phases,

phase 1 and phase 2. The number of phases can be selected by the phase bit,

(R/X)PHASE, in the RCR and XCR. The number of elements per frame and

bits per element can be independently selected for each phase via

(R/X)FRLEN(1/2) and (R/X)WDLEN(1/2), respectively. Figure 11–8 shows a

frame in which the first phase consists of two elements of 12 bits each followed

by a second phase of three elements of 8 bits each. The entire bit stream in

the frame is contiguous; no gaps exist either between elements or phases.

Table 11–9 shows the fields in the receive/transmit control registers (RCR/

XCR) that control the frame length and element length for each phase for both

the receiver and the transmitter. The maximum number of elements per frame

is 128 for a single-phase frame and 256 elements in a dual-phase frame. The

number of bits per element can be 8, 12, 16, 20, 24, or 32.

Note:

For a dual-phase frame with internally generated frame sync, the maximum

number of elements per phase depends on the word length. This is because

the frame period, FPER is only 12-bits wide and, therefore, provides 4 096

bits per frame. Hence, the maximum number of 128 elements per single-

phase frame for a total of 256 elements per dual-phase frame applies only

when the WDLEN is 16-bits.