L-827e.A3 phyCORE-i.MX 6UL/ULL Hardware Manual

© PHYTEC Messtecknik GmbH

51

phyCORE

‑

Connector X1. The SPI interface provides one chip select signal. The Enhanced Configurable SPI (eCSPI) of

the i.MX 6UL/ULL has up to four separate modules (eCSPI1, eCSPI2, eCSPI3 and eCSPI4) which support data rates of

up to 52 Mbit/s. The interface signals of the third module (eCSPI3) are made available on the phyCORE-Connector.

These modules are master/slave configurable. The following table lists the SPI signals on the phyCORE-Connector.

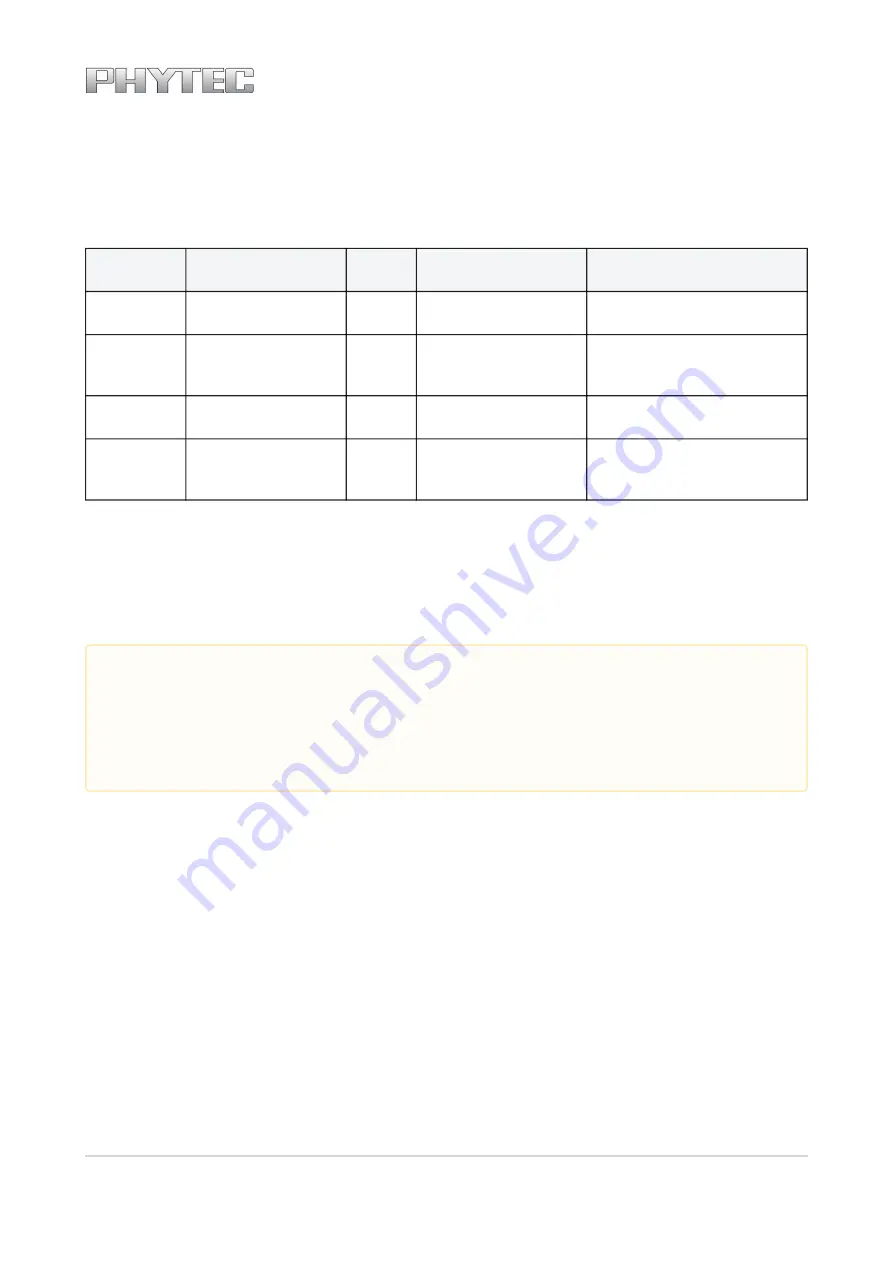

TABLE 21: SPI Interface Signal Location

Pin #

Signal

ST

Voltage Domain

Description

109

X_ECSPI3_CLK

I/O

VDD_3V3

ECSPI3 clock

110

X_ECSPI3_MOSI

I/O

VDD_3V3

ECSPI3 master output/slave

input

111

X_ECSPI3_SS0

I/O

VDD_3V3

ECSPI3 chip select 0

112

X_ECSPI3_MISO

I/O

VDD_3V3

ECSPI3 master input/slave

output

11.5 I

2

C Interface

The Inter-Integrated Circuit (I

2

C) interface is a two-wire, bidirectional serial bus that provides a simple and efficient

method for data exchange among devices. The i.MX 6UL/ULL contains up to four identical and independent

Multimaster fast-mode I

2

C modules. The interface of the first module (I2C1) is available on the phyCORE-Connector.

The following table lists the I

2

C port 1 on the phyCORE-Connector.

Note

When using the I2C1 interface it must be considered that the on-board I²C EEPROM is connected to this

interface, too (

). Pull up resistors are already populated on the module. To ensure the

proper functioning of the I

2

C interface external pull resistors matching the load at the interface should not

be connected on your carrier board. If too many devices or signal length increases very much, use an I²C

buffer to extend the I²C bus.