L-827e.A3 phyCORE-i.MX 6UL/ULL Hardware Manual

© PHYTEC Messtecknik GmbH

49

11.3 Ethernet Interface

Connection of the phyCORE

‑

i.MX 6UL/ULL to the world wide web or a local area network (LAN) is possible using the

onboard Ethernet PHY at U2. It is connected to the RMII interface of the i.MX 6UL/ULL. The PHY operates with a data

transmission speed of 10 Mbit/s or 100 Mbit/s. The second Ethernet interface of the i.MX 6UL/ULL is available as an

RMII interface at the phyCORE

‑

Connector to allow the connection of an external PHY (

11.3.1 Ethernet PHY (U2)

With an Ethernet PHY mounted at U2, the phyCORE

‑

i.MX 6UL/ULL has been designed for use in 10Base-T and

100Base-T networks. The 10/100Base-T interface with its LED signals extends to the phyCORE

‑

Connector X1.

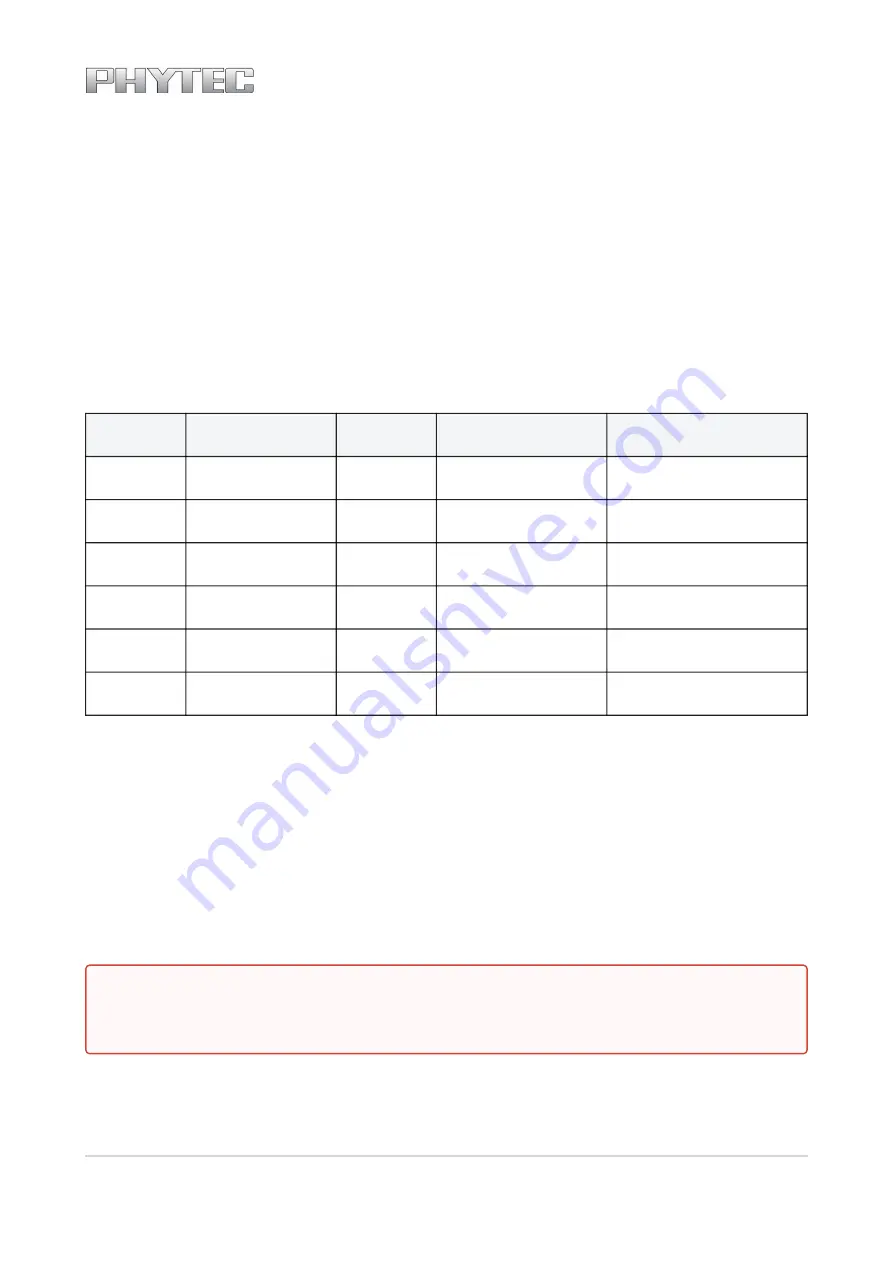

TABLE 19: Location of the Ethernet PHY Signals

Pin #

Signal

ST

Voltage Domain

Description

12

X_E

ETH_O

VDD_3V3

ETH1 data A+/t

13

X_ENET1_TX-

ETH_O

VDD_3V3

ETH1 data A-/transmit-

14

X_E

ETH_I

VDD_3V3

ETH1 data B+/

15

X_ENET1_RX-

ETH_I

VDD_3V3

ETH1 data B-/receive-

16

X_ETH1_LED1

I/O

VDD_3V3

ETH1 SPEED /LED activity

17

X_ETH1_LED0

I/O

VDD_3V3

ETH1 NWAYEN /LED link

The on-board Ethernet PHY supports HP Auto-MDIX technology, eliminating the need for the consideration of a

direct-connect LAN or cross-over patch cable. It detects the TX and RX pins of the connected device and

automatically configures the PHY TX and RX pins accordingly. The Ethernet PHY also features an Auto-negotiation

to automatically determine the best speed and duplex mode.

The Ethernet PHY is connected to the ENET1 RMII interface of the i.MX 6UL/ULL. Please refer to the

i.MX 6UL/ULL

Reference Manual

for more information about this interface.

In order to connect the module to an existing 10/100 Base-T network, some external circuitry is required. The

required termination resistors on the analog signals (ETH1_A±, ETH1_B±) are integrated into the chip, so there is no

need to connect external termination resistors to these signals. Connection to external Ethernet magnetics should

be done using very short signal traces. The A+/A- and B+/B- signals should be routed as 100 Ohm differential pairs.

The same applies to the signal lines after the transformer circuit. The carrier board layout should avoid any other

signal lines crossing the Ethernet signals.

Warning

Please see the datasheet of the Ethernet PHY when designing the Ethernet transformer circuitry, or

request the schematic of the applicable carrier board (phyBOARD

‑

Segin i.MX 6UL/ULL) as reference.