4. Addressing > I/O Space

32

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

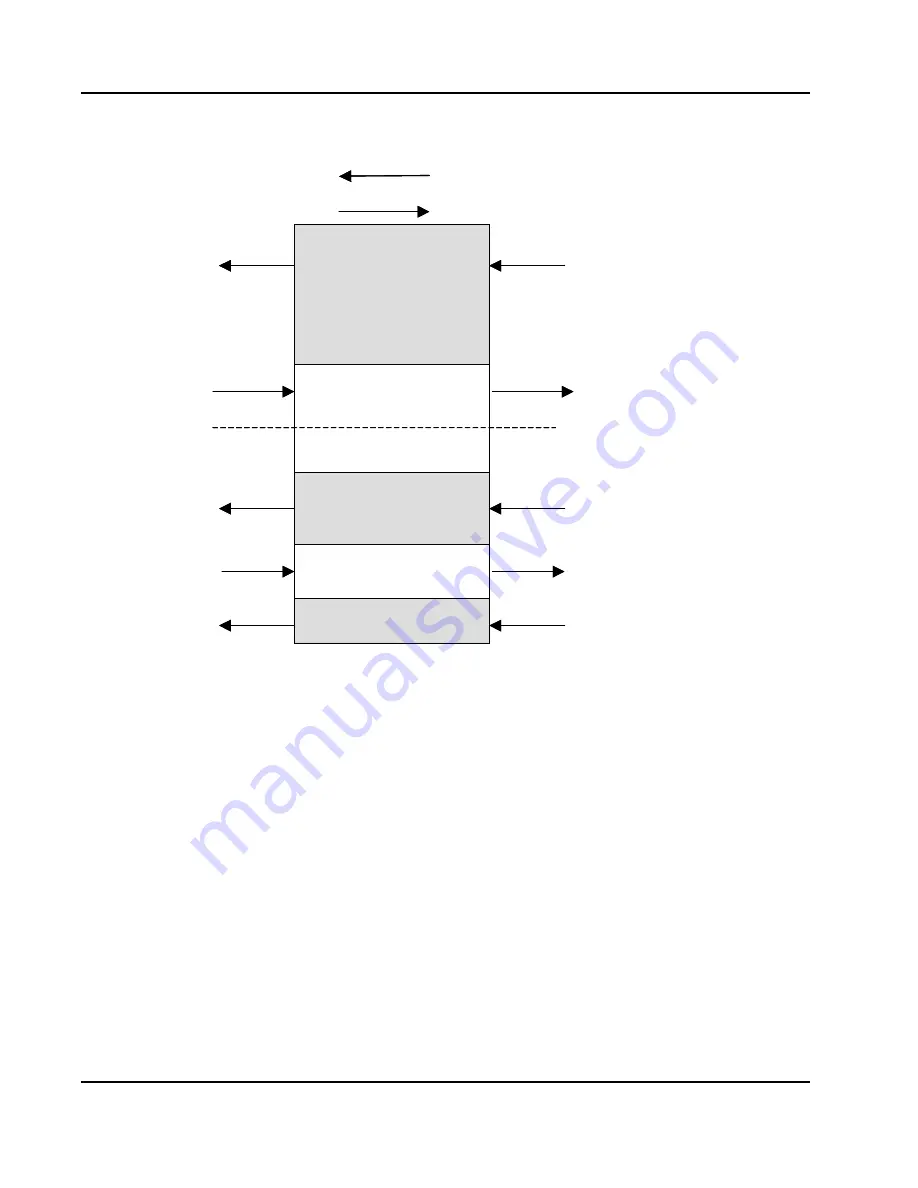

Figure 10: 64-bit Prefetchable Memory Address Range

4.4

I/O Space

I/O Base, I/O Limit, I/O Base Upper 16 Bits, and I/O Limit Upper 16 Bits registers in the PEB383

configuration header specify an address range that is used by the bridge to determine whether to

forward I/O read and I/O write transactions across the bridge. If the address specified by the I/O Base

and I/O Base Upper 16 Bits registers is set to a value greater than the address specified by the I/O Limit

and I/O Limit Upper 16 Bits registers, the address range is disabled.

The response of the bridge to I/O transactions is controlled by the following configuration register bits:

•

I/O Space Enable bit in

“PCI Control and Status Register”

•

Bus Master Enable bit in

“PCI Control and Status Register”

•

ISA Enable bit in

“PCI Bridge Control and Interrupt Register”

•

VGA Enable bit in

“PCI Bridge Control and Interrupt Register”

The I/O Enable

bit must be set for any I/O transaction to be forwarded downstream. If this bit is not set,

all I/O transactions on the PCI bus are forwarded to the PCIe link. If this bit is not set, all PCIe

Interface I/O requests are completed with Unsupported Request status.

Primary Interface

Downstream

Upstream

Memory Mapped I/O

4 GB Boundary

4 GB Boundary

Secondary Interface

Prefetchable Memory

Primary Interface

Downstream

Upstream

Memory Mapped I/O

4 GB Boundary

4 GB Boundary

Secondary Interface

Prefetchable Memory