3. Data Path > Buffer Structure

25

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

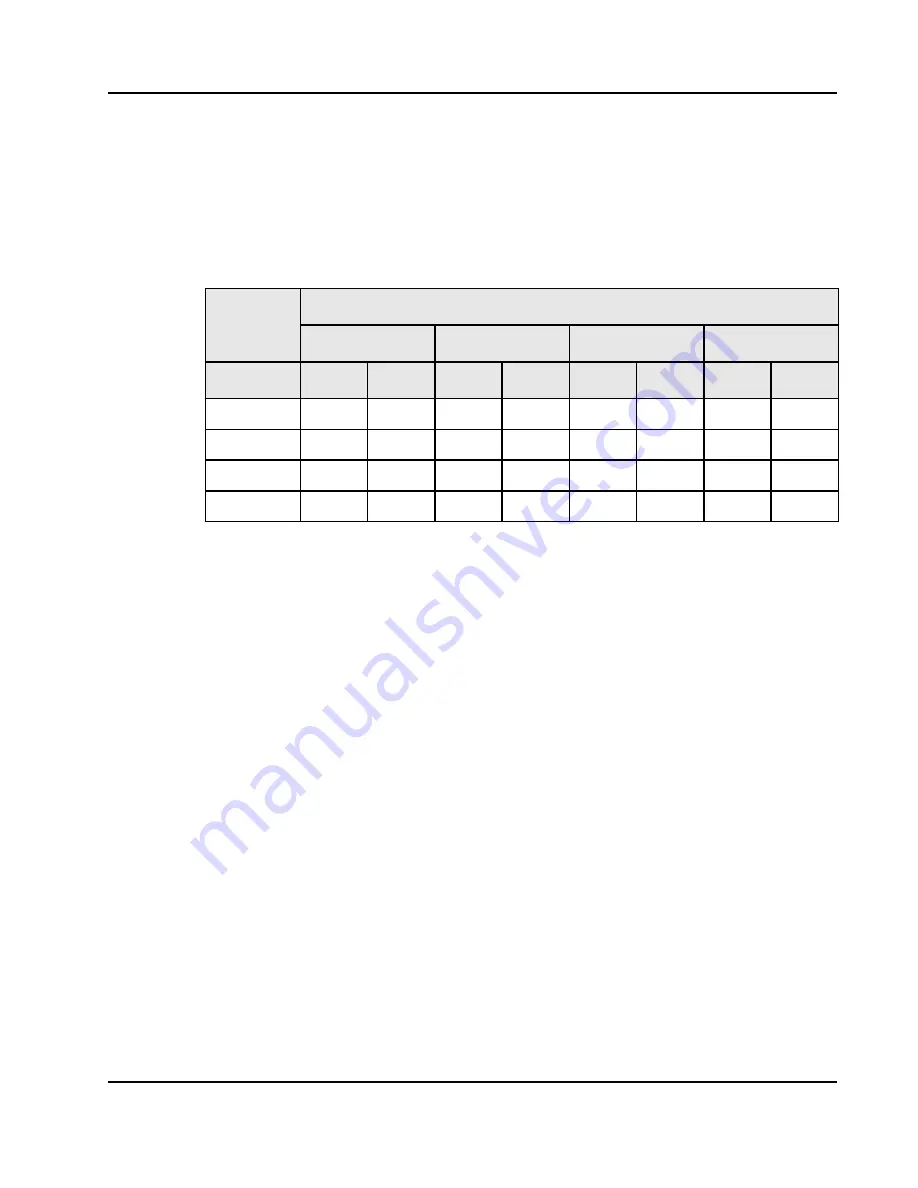

By default the programed allocation amount of buffers that are allocated is equal to the prefetch size. In

order to prevent one device from consuming all the buffers, the allocation size can be programmed to

be less than the prefetch size. For example, if the prefetch size was set to 1 KB, then only one

outstanding request would result, as once all the buffers are allocated no more requests can be sent. The

allocation size can be programmed to be 512 bytes (or 256, 128) so that 1, 2, or 4 outstanding requests

are possible (see MAX_BUF_ALOC bits in the

“Upstream Posted Write Threshold Register”

).

The requests are sent in order — small requests do not pass large requests — as completion buffers are

unallocated. Otherwise, this would cause unfairness since smaller requests could block larger requests.

The completions can occur out of order; that is, the bridge always responds with completion data if it is

in the buffers. This is done to improve throughput when there are multiple outstanding read requests.

3.3.1.1

Non-posted Write Buffer

The PEB383 supports one non-posted write transaction. Similar to read requests, its request

information is stored in one of the eight request queue entries, and its data is stored in a 32-bit register.

Non-posted write requests are forwarded onto the PCIe Core in two PCIe clock cycles. Request

information is forwarded in the first cycle, while 32-bit data is forwarded in the second cycle.

3.3.2

Upstream Posted Buffer

The upstream posted buffer is a FIFO of size 512 bytes that stores memory write transactions that

originate on the PCI Interface and are destined to devices on PCIe Interface. The PEB383 completes

the posted transactions on the originating bus before forwarding them to the PCIe Interface. Unlike the

read buffers, the amount of space assigned to each transaction is dynamic. A single transaction can use

512 bytes of buffer space. The PEB383 translates all types of memory write transactions from the PCI

Interface to memory write requests on the PCIe Interface. The PEB383 terminates a new transaction

with retry and an active transaction with disconnect if sufficient buffer space is not available.

The PEB383 uses an 8-deep request FIFO to store the request information, including first and last

Dwords byte enables of the received transactions.

Table 8: Completion Buffer Allocation

Bit setting

----->

MAX_BUF_ALOC

0b11

0b10

0b01

0b11

Prefetch

ALOC

a

a.

Completion buffer allocation in bytes.

ORR

b

b.

Number of Outstanding Read Requests.

ALOC

ORR

ALOC

ORR

ALOC

ORR

1024 bytes

1024

1

512

2

256

4

256

4

512 bytes

512

2

512

2

256

4

256

4

256 bytes

256

4

256

4

256

4

256

4

128 bytes

128

4

128

4

128

4

128

4