14. Register Descriptions > PCI Capability Registers

171

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

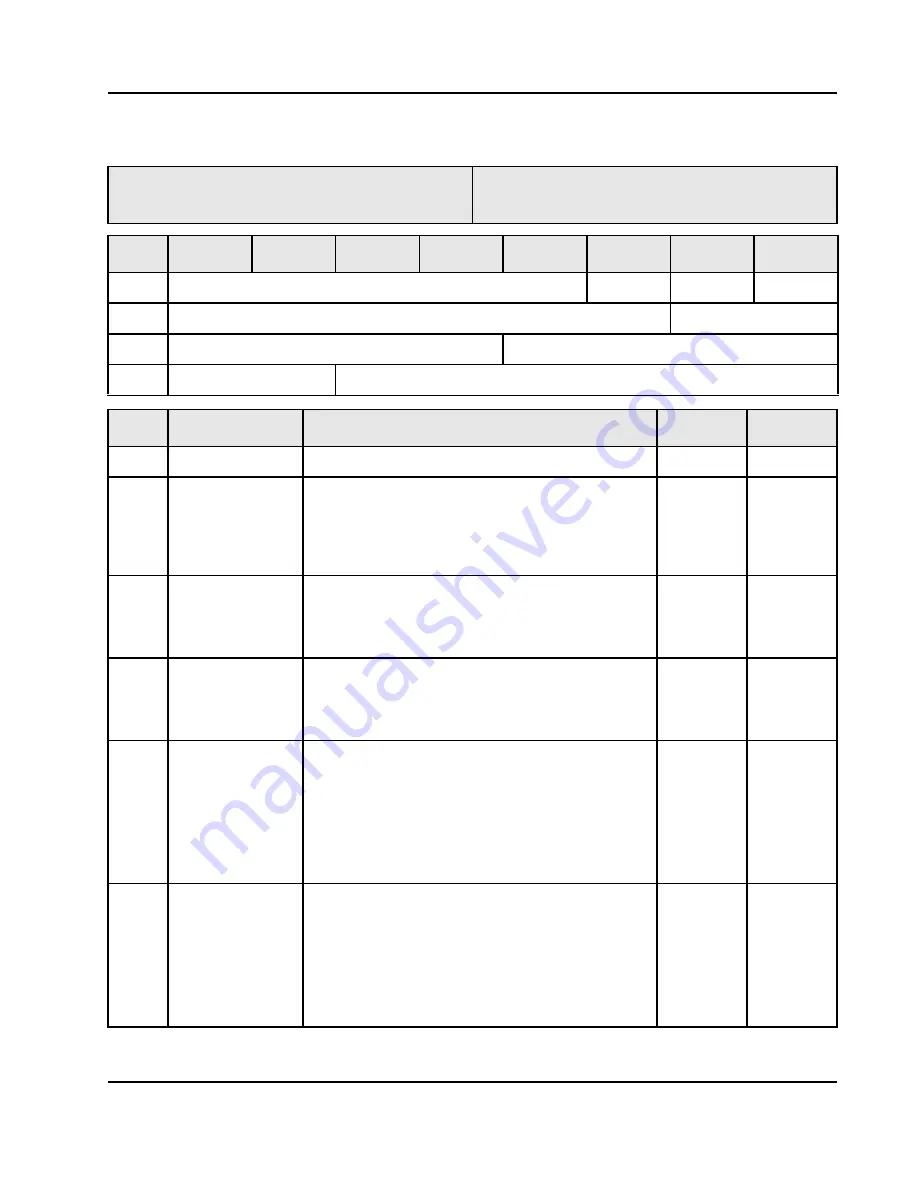

14.5.10

Prefetch Control Register

Register name: PREF_CTRL

Reset value: 0x0300_0041

Register offset: 0x0BC

Bits

7

6

5

4

3

2

1

0

31:24

Reserved

P_MR

P_MRL

P_MRM

23:16

MRL_66

MRL_33

15:08

MRL_33

MRM_66

07:00

MRM_66

MRM_33

Bits

Name

Description

Type

Reset value

31:27

Reserved

Reserved

R

0x00

26

P_MR

0 = The PEB383 fetches a Dword of data in case of 32-bit

PCI data bus mode.

1 = The PEB383 prefetches as per the value specified in

MRL_66/MRL_33 fields on behalf of the PCI master for

memory read command.

R/W

0

25

P_MRL

0 = The PEB383 prefetches one cacheline of data.

1 = The PEB383 prefetches as per the value specified in

MRL_66/MRL_33 fields on behalf of the PCI master for

memory read line command.

R/W

1

24

P_MRM

0 = The PEB383 prefetches two cachelines of data.

1 = The PEB383 prefetches as per the value specified in

MRM_66/MRM_33 fields on behalf of PCI master for

memory read multiple command.

R/W

1

23:18

MRL_66

This bit indicates the threshold parameter for Memory read

line and memory read commands in 66-MHz PCI mode. Unit

is 64-byte chunk.

6’h00 = 64 bytes

6’h01 = 128 bytes

...

6’h3F = 4096 bytes

R/W

0x00

17:12

MRL_33

This bit indicates the threshold parameter for Memory read

line and memory read commands in 33-MHz PCI mode. Unit

is 64-byte chunk.

6’h00 = 64 bytes

6’h01 = 128 bytes

...

6’h3F = 4096 bytes

R/W

0x00