14. Register Descriptions > Register Map

131

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

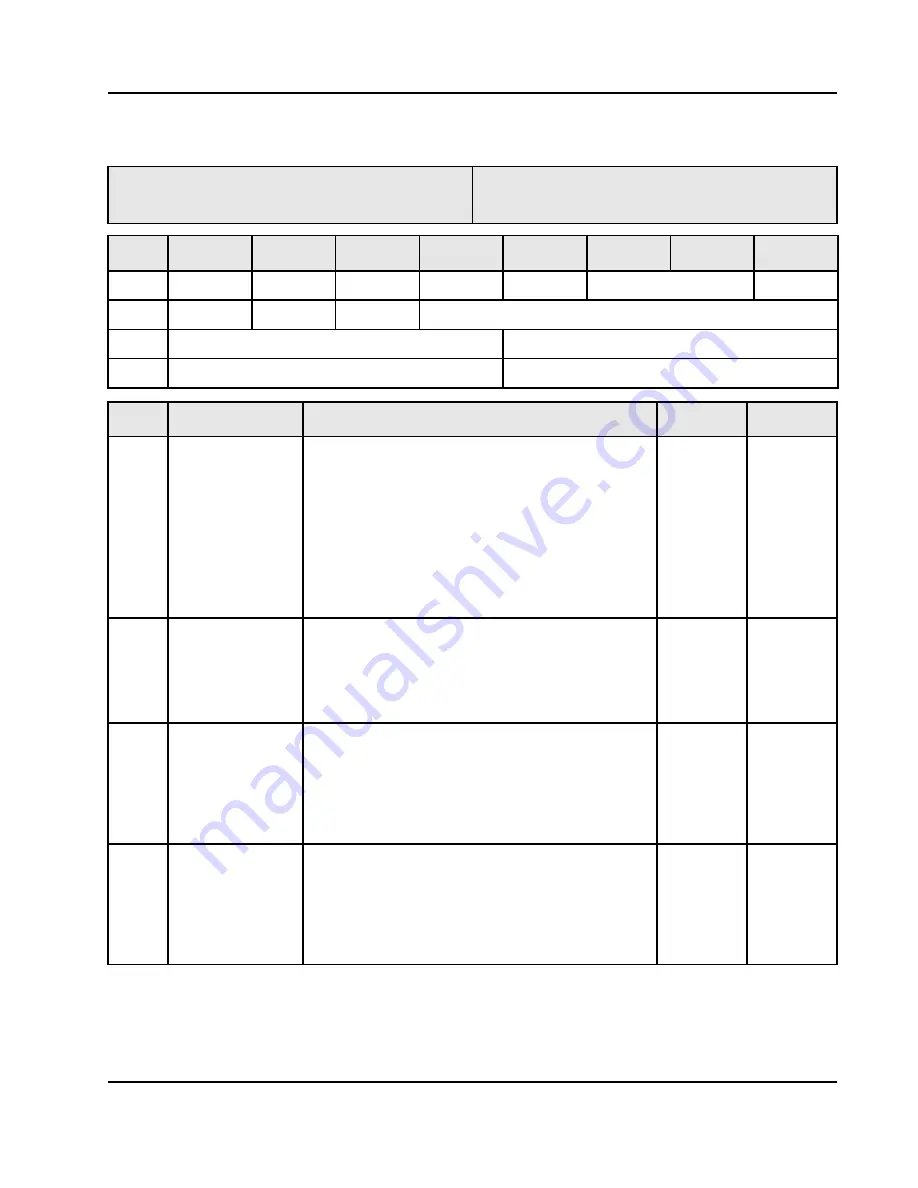

14.3.6

PCI Secondary Status and I/O Limit and Base Register

Register name: PCI_MISC1_P

Reset value: 0x02A0_0101

Register offset: 0x01C

Bits

7

6

5

4

3

2

1

0

31:24

D_PE

S_SERR

R_MA

R_TA

S_TA

DEVSEL

MDP_D

23:16

TFBBC

Reserved

DEV66

Reserved

15:08

IO_LA

ADD_CAP1

07:00

IO_BA

ADD_CAP2

Bits

Name

Description

Type

Reset value

31

D_PE

Data Parity Error Detected

This bit reports the detection of an address or data parity

error on the PEB383’s PCI Interface. The PEB383 sets this

bit when it detects one of the following:

• Address parity error as a potential target

• Data parity error as a target of a write transaction

• Data parity error as a master of a read transaction

0 = Device did not detect a parity error.

1 = Device detected a parity error.

R/W1C

0

30

S_SERR

Received System Error

This bit reports the assertion of PCI_SERRn on the PCI

Interface.

1 = PCI_SERRn was detected on the PCI Interface.

0 = PCI_SERRn was not detected.

R/W1C

0

29

R_MA

Received Master Abort

This bit reports the detection of a Master-Abort termination

by the PEB383 when it is the master of a transaction on its

PCI Interface.

0 = No Master-Abort detected.

1 = Master-Abort detected on the PCI Interface.

R/W1C

0

28

R_TA

Received Target Abort

This bit reports the detection of a Target-Abort termination

by the PEB383 when it is the master of a transaction on its

PCI Interface.

0 = No Target-Abort detected.

1 = Target-Abort detected on the PCI Interface.

R/W1C

0