2. Signal Descriptions > PCI Interface Signals

17

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

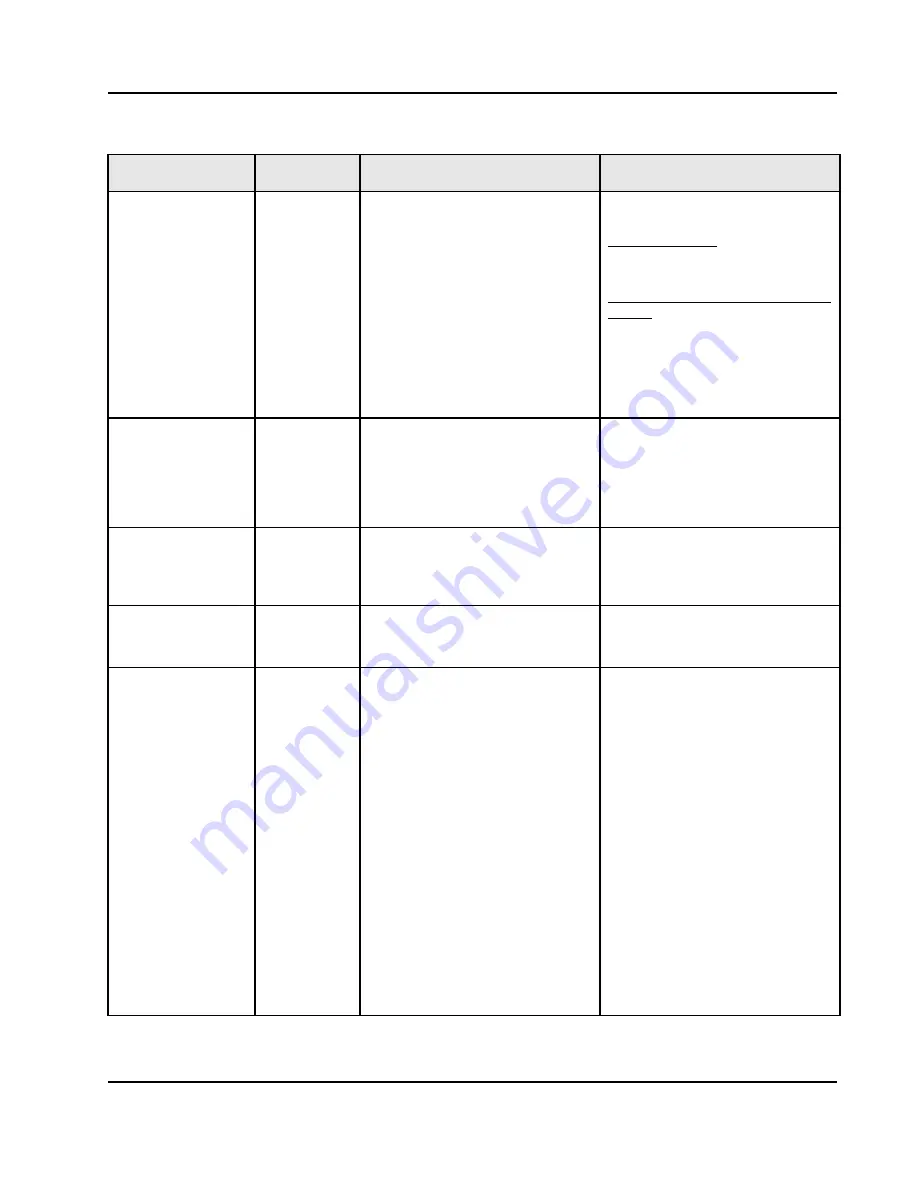

PCI_M66EN

PCI In

66-MHz Enable. This signal enables the

PCI Interface for 66-MHz operation.

0 = 33-MHz operation

1 = 66-MHz operation

PCI_M66EN is used only in master

clocking mode.

Embedded designs

Tied to ground for 33-MHz operation;

otherwise, pull up to VIO_PCI.

Bused designs using PCI slots for add-

in cards

Place a 10K pull-up resistor (to

VIO_PCI) on PCI_M66EN and route the

signal from slot to slot.

In slave clocking mode, PCI_M66EN

can be tied to ground.

PCI_PAR

PCI Bidir

Parity. This signal carries even parity

across PCI_AD[31:0] and

PCI_CBEn[3:0]. The bus master

asserts this signal for the address and

write data phases. The bus target

asserts it for read data phases.

No pull-up or pull-down resistor is

required.

PCI_PERRn

PCI Bidir

Parity Error. This signal indicates a

parity error occurred during the current

data phase. The bus target that

receives the data asserts this signal.

Pull up (8.2K) to VIO_PCI.

PCI_PMEn

PCI In

Power Management Event. This signal

indicates a power management event

occurred (see

Pull up (8.2K) to VIO_PCI.

PCI_REQn[3:0]

PCI In

PCI Bidir

Bus Request. These signals are used to

request access to the PCI bus. They are

used differently, however, depending on

whether or not the PEB383 PCI arbiter

is used. If the PCI arbiter is used, then

PCI_REQn[3:0] are inputs used by

external masters to request access to

the bus.

If an external arbiter is used,

PCI_REQn[0] is an output used by the

PEB383 to request access to the bus,

while PCI_REQn[3:1] should be pulled

high, as they are still inputs.

The input/output mode is controlled by

bit[9] of

“PCI Miscellaneous 0 Register”

.

Note: The PCI bus arbiter can be placed

on the last bus master by bit[8] of

Miscellaneous 0 Register” on page 129

.

Pull up (8.2K) to VIO_PCI.

Table 3: PCI Interface Signals

(Continued)

Name

Pin Type

Description

Design Recommendation