> PCIe and SerDes Control and Status Registers

208

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

14.9.2

PCIe Per-Lane Transmit and Receive Registers

14.9.3

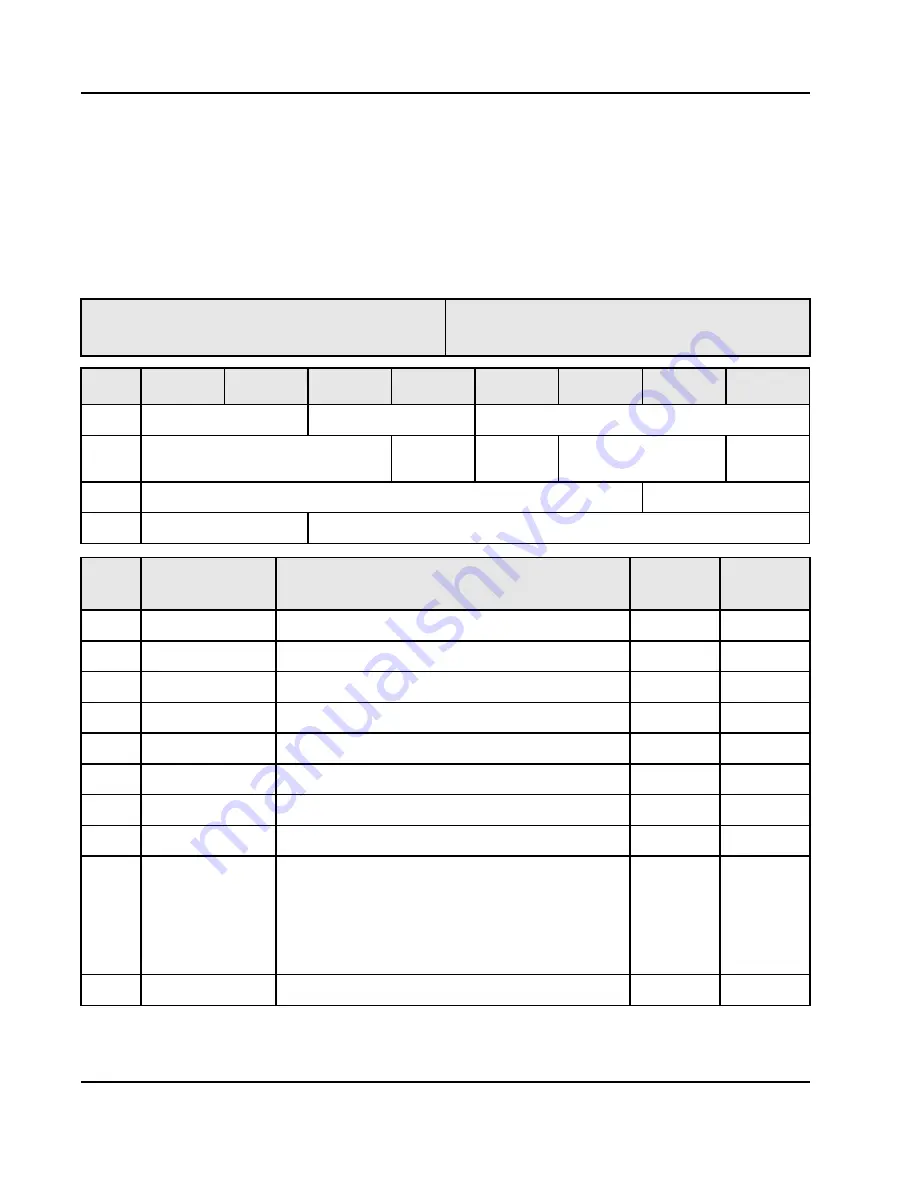

PCIe Transmit and Receive Status Register

This register reflects the default state of the SerDes transmit and receive control inputs at power-up. Its

reset value depends on various inputs. When its accompanying override registers are used, however

(see

“PCIe Output Status and Transmit Override Register”

“PCIe Receive and Output Override

), the relevant status bits are no longer valid.

Register name: PCIE_TXRX_STAT

Reset value: Undefined

Register offset: 0x000

Bits

7

6

5

4

3

2

1

0

31

:

24

Reserved

LOS_CTL

Reserved

23

:

16

RX_EQ_VAL

Reserved

RX_ALIGN

_EN

Reserved

HALF_

RATE

15:08

Reserved

TX_BOOST

07:00

TX_BOOST

Reserved

Bits

Name

Description

Type

Reset

Value

31:30

Reserved

Reserved

R

01

29:28

LOS_CTL

LOS filtering mode control

R

Undefined

27:24

Reserved

Reserved

R

Undefined

23:21

RX_EQ_VAL

Receive Equalization control

R

0b010

20

Reserved

Reserved

R

0

18:17

Reserved

Reserved

R

Undefined

16

HALF_RATE

Digital half-rate data control

R

Undefined

15:10

Reserved

Reserved

R

100000

9:6

TX_BOOST

Transmit Boost control

Programmed boost value (ratio of drive level of transition bit

to non-transition bit) is:

boost = -20*log(1-(tx_boost[3:0]+0.5)/32)dB, except that

setting TX_BOOST to 0 produces 0dB of boost. This

produces results up to 5.75dB in steps of ~0.37dB.

R

0b1011

5:0

Reserved

Reserved

R

Undefined