> PCIe and SerDes Control and Status Registers

210

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

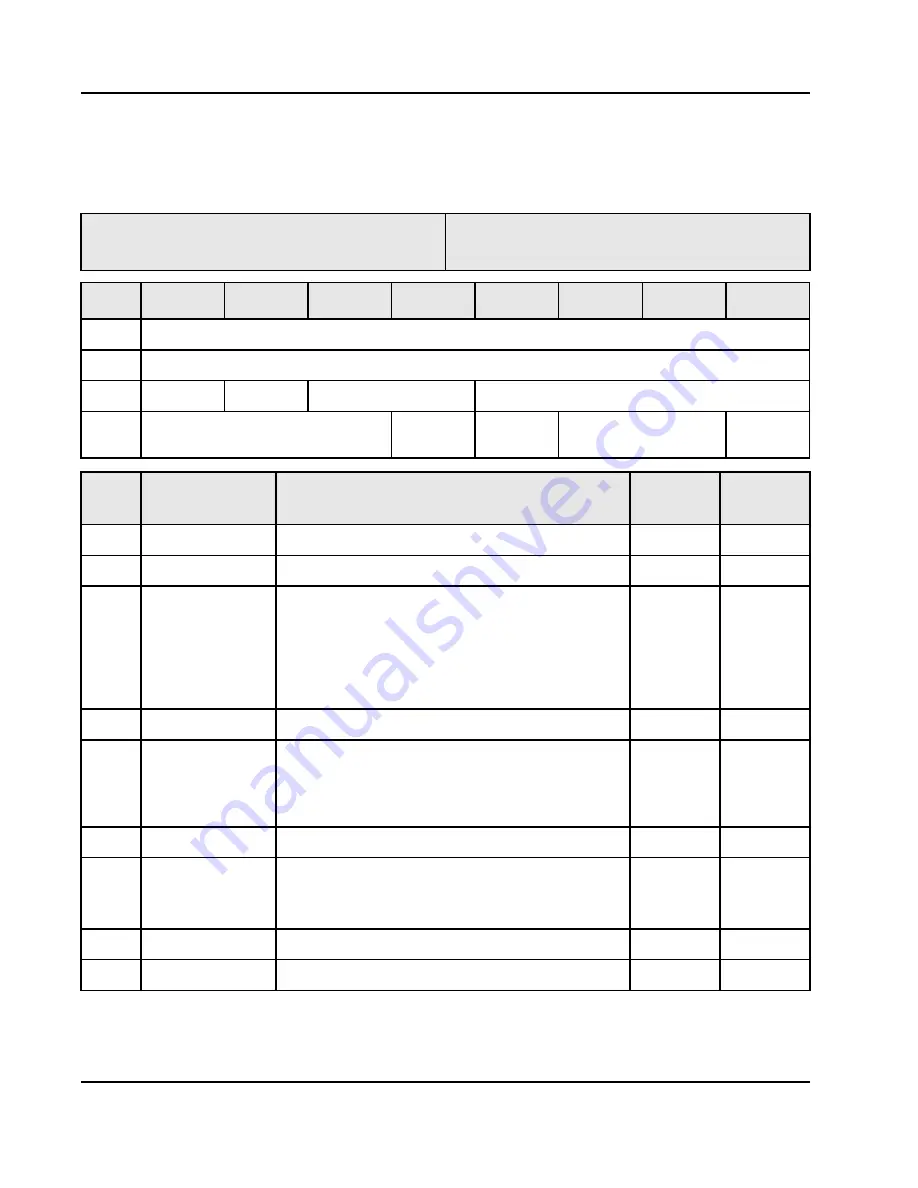

14.9.5

PCIe Receive and Output Override Register

This register provides a method for overriding the values of LOS_CTL, RX_EQ_VAL, and

RX_ALIGN_EN in the

“PCIe Transmit and Receive Status Register”

.

Register name: PCIE_RX_OVRD

Reset value: Undefined

Register offset: 0x008

Bits

7

6

5

4

3

2

1

0

31

:

24

ReservedP

23

:

16

ReservedP

15:08

ReservedP

OVRD_2

LOS_CTL

ReservedP

07:00

RX_EQ_VAL

ReservedP

RX_ALIGN

_EN

ReservedP

HALF_

RATE

Bits

Name

Description

Type

Reset

Value

31:15

ReservedP

Preserve state on writes.

R

Undefined

14

OVRD_2

Enable override of relevant bits 0:13 in this register.

R/W

0

13:12

LOS_CTL

LOS filtering mode control

00 = Disabled

01-10 = Reserved

11 = Heavy filtering. The LOS signal is synchronous to the

output of the prescaler. Heavy filtering means 128 +/- 5

cycles of no signal for LOS to be asserted.

R/W

01

11:8

ReservedP

Preserve state on writes.

R/W

Undefined

7:5

RX_EQ_VAL

Receive Equalization control

Internal linear equalizer boost is approximately =

(rx1)*0.5dB

Example: 3’b100 = 2.5dB boost

R/W

000

4

ReservedP

Preserve state on writes.

R/W

1

3

RX_ALIGN_EN

Enable Word Alignment

0 = Alignment (framer) disabled

1 = Alignment enabled

R/W

1

2:1

ReservedP

Preserve state on writes.

R/W

11

0

HALF_RATE

Digital half-rate data control

R/W

0