14. Register Descriptions > Register Map

124

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

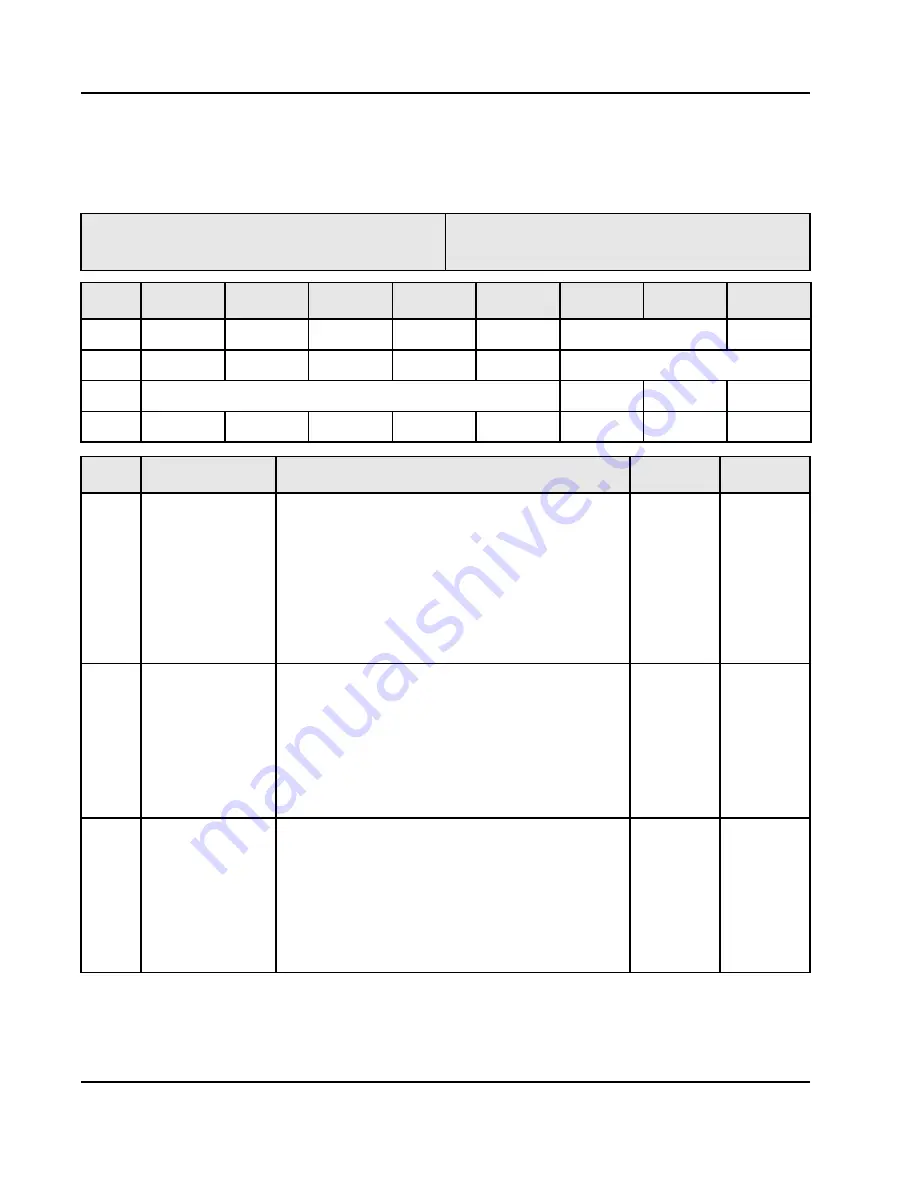

14.3.2

PCI Control and Status Register

This register defines configurable parameters for how devices interact with the PCI bus, and indicates

status information for PCI bus events.

Register name: PCI_CSR

Reset value: 0x_0010_0000

Register offset: 0x004

Bits

7

6

5

4

3

2

1

0

31:24

D_PE

S_SERR

R_MA

R_TA

S_TA

DEVSEL

MDP_D

23:16

TFBBC

Reserved

DEV66

CAP_L

INT_STAT

Reserved

15:08

Reserved

INT_DIS

MFBBC

SERR_EN

07:00

WAIT

PERESP

VGAPS

MWI_EN

SC

BM

MS

IOS

Bits

Name

Description

Type

Reset value

31

D_PE

Detected Parity Error

This bit is set by the bridge whenever it receives a poisoned

TLP or a TLP with bad ECRC (Read Completion or Write

Request) on the PCIe Interface, regardless of the state the

Parity Error Response bit in the Command register.

0 = Data poisoning and bad ECRC not detected by the

bridge on its PCIe Interface

1 = Data poisoning or bad ECRC detected by the bridge on

its PCIe Interface

R/W1C

0

30

S_SERR

Signaled System Error

This bit is set when the bridge sends an ERR_FATAL or

ERR_NONFATAL message to the Root Complex and the

SERR# Enable bit is set in the Command register.

0 = Neither ERR_FATAL nor ERR_NONFATAL transmitted

on the PCIe Interface

1 = ERR_FATAL or ERR_NONFATAL transmitted on the

PCIe Interface

R/W1C

0

29

R_MA

Received Master-Abort

This bit is set when the bridge receives a Completion with

Unsupported Request Completion Status on its PCIe

Interface.

0 = Unsupported Request Completion Status not received

on the PCIe Interface

1 = Unsupported Request Completion Status received on

the PCIe Interface

R/W1C

0