UG-498

ADuCM320 Hardware Reference Manual

Rev. C | Page 106 of 196

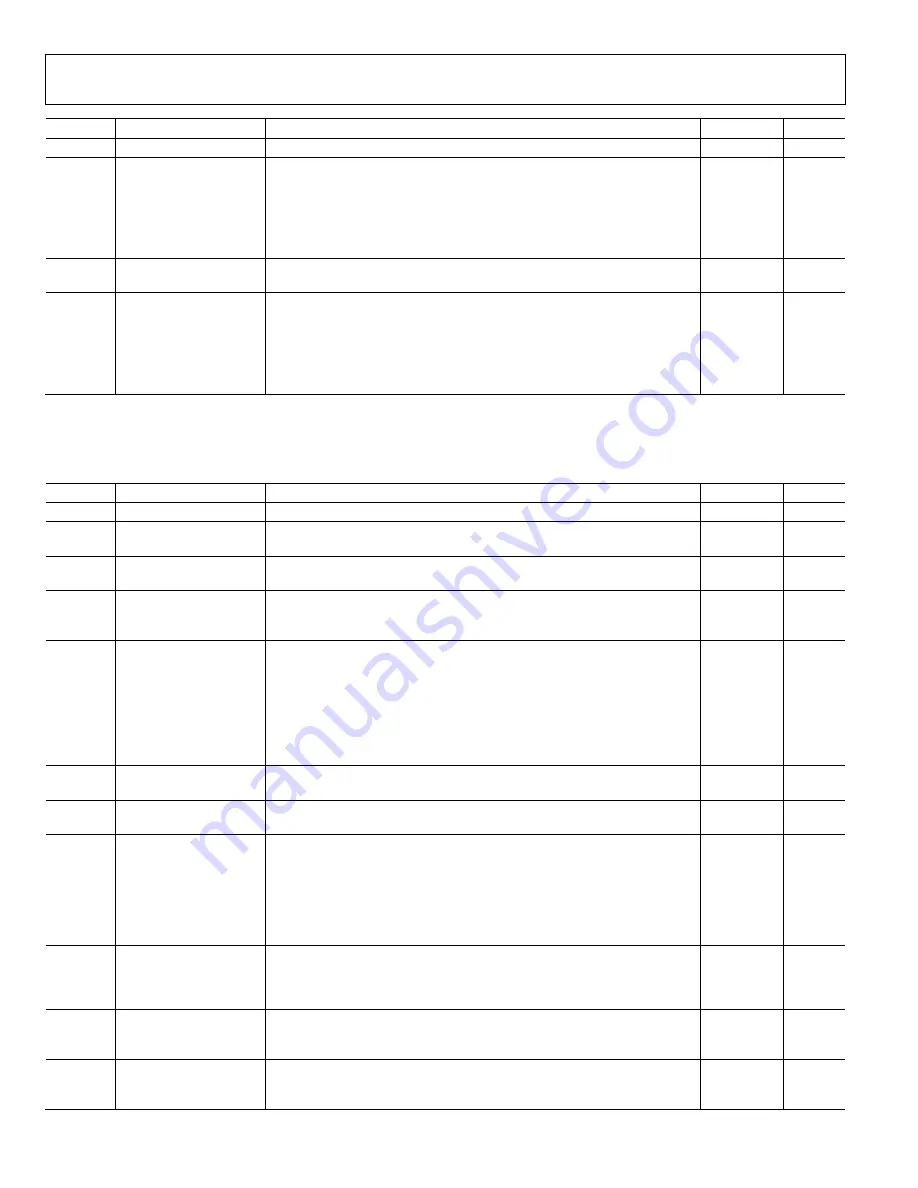

Bits

Bit Name

Description

Reset

Access

3

RESERVED

Reserved. A value of 0 should be written to this bit.

0x0

RW

2

LOOPBACK

Internal loopback enable. Note that is also possible for the master to loop

back a transfer to the slave as long as the device address corresponds, that

is, external loopback.

0x0

RW

0: SCL and SDA out of the device are not muxed onto their corresponding

inputs.

1: SCL and SDA out of the device are muxed onto their corresponding inputs.

1

COMPETE

Start back-off disable. Setting this bit enables the device to compete for

ownership even if another device is currently driving a START condition.

0x0

RW

0

MASEN

Master enable. The master should be disabled when not in use, because

this gates the clock to the master and saves power. This bit should not be

cleared until a transaction has completed (see the TCOMP bit in the master

status register).

0x0

RW

0: master is disabled

1: master is enabled

Master Status Register

Address: 0x40003004, Reset: 0x6000, Name: I2C0MSTA

Table 137. Bit Descriptions for I2C0MSTA

Bits

Bit Name

Description

Reset

Access

15

RESERVED

Reserved.

0x0

R

14

SCL_FILTERED

State of SCL line. This bit is the output of the glitch-filter on SCL. SCL is

always pulled high when undriven.

0x1

R

13

SDA_FILTERED

State of SDA line. This bit is the output of the glitch-filter on SDA. SDA is

always pulled high when undriven.

0x1

R

12

MTXUFLOW

Master transmit underflow. Asserts when the I2C0 master ends the

transaction due to Tx-FIFO empty condition. This bit is asserted only when

the IENMTX bit is set.

0x0

RC

11

MSTOP

STOP driven by this I2C0 Master. Asserts when this I2C0 master drives a

STOP condition on the I2C0 bus. This bit, when asserted, can indicate a

Transaction completion, Tx-underflow, Rx-overflow or a NACK by the slave.

This is different from the TCOMP as this bit is not asserted when the STOP

condition occurs due to any other I2C0 master. No interrupt is generated

for the assertion of this bit. However, if IENCMP is 1, every STOP condition

generates an interrupt and this bit can be read. When this bit is read, it

clears status.

0x0

RC

10

LINEBUSY

Line is busy. Asserts when a START is detected on the I2C0 bus. Deasserts

when a STOP is detected on the I2C0 bus.

0x0

R

9

MRXOF

Master receive FIFO overflow. Asserts when a byte is written to the receive

FIFO when the FIFO is already full. When the bit is read, it clears status.

0x0

RC

8

TCOMP

Transaction complete or stop detected. Transaction complete. This bit

asserts when a STOP condition is detected on the I2C0 bus. If IENCMP is 1,

an interrupt is generated when this bit asserts. This bit only asserts if the

master is enabled (MASEN = 1). This bit should be used to determine when it is

safe to disable the master. It can also be used to wait for another master

transaction to complete on the I2C0 bus when this master loses arbitration.

When this bit is read, it clears status. This bit can drive an interrupt.

0x0

RC

7

NACKDATA

ACK not received in response to data write. This bit asserts when an ACK is

not received in response to a data write transfer. If IENACK is 1, an interrupt

is generated when this bit asserts. This bit can drive an interrupt. This bit is

cleared on a read of the I2C0MSTA register.

0x0

RC

6

MBUSY

Master busy. This bit indicates that the master state machine is servicing a

transaction. It is cleared if the state machine is idle or another device has

control of the I2C0 bus.

0x0

R

5

ALOST

Arbitration lost. This bit asserts if the master loses arbitration. If IENALOST

is 1, an interrupt is generated when this bit asserts. This bit is cleared on a

read of the I2C0MSTA register. This bit can drive an interrupt.

0x0

RC