-

15

-

6.

CPU

Interface

6-1.

Setting

the

CPU

interface

type

These

PCLs

contain

the

following

4

CPU

interface

types,

in

order

to

facilitate

connection

to

various

CPUs.

To

select

a

specific

type,

use

the

IF0

and

IF1

terminals.

Shown

below

are

some

circuit

examples.

To

use

some

other

CPU,

select

the

appropriate

interface

after

referring

to

section

"12-5.

AC

characteristics."

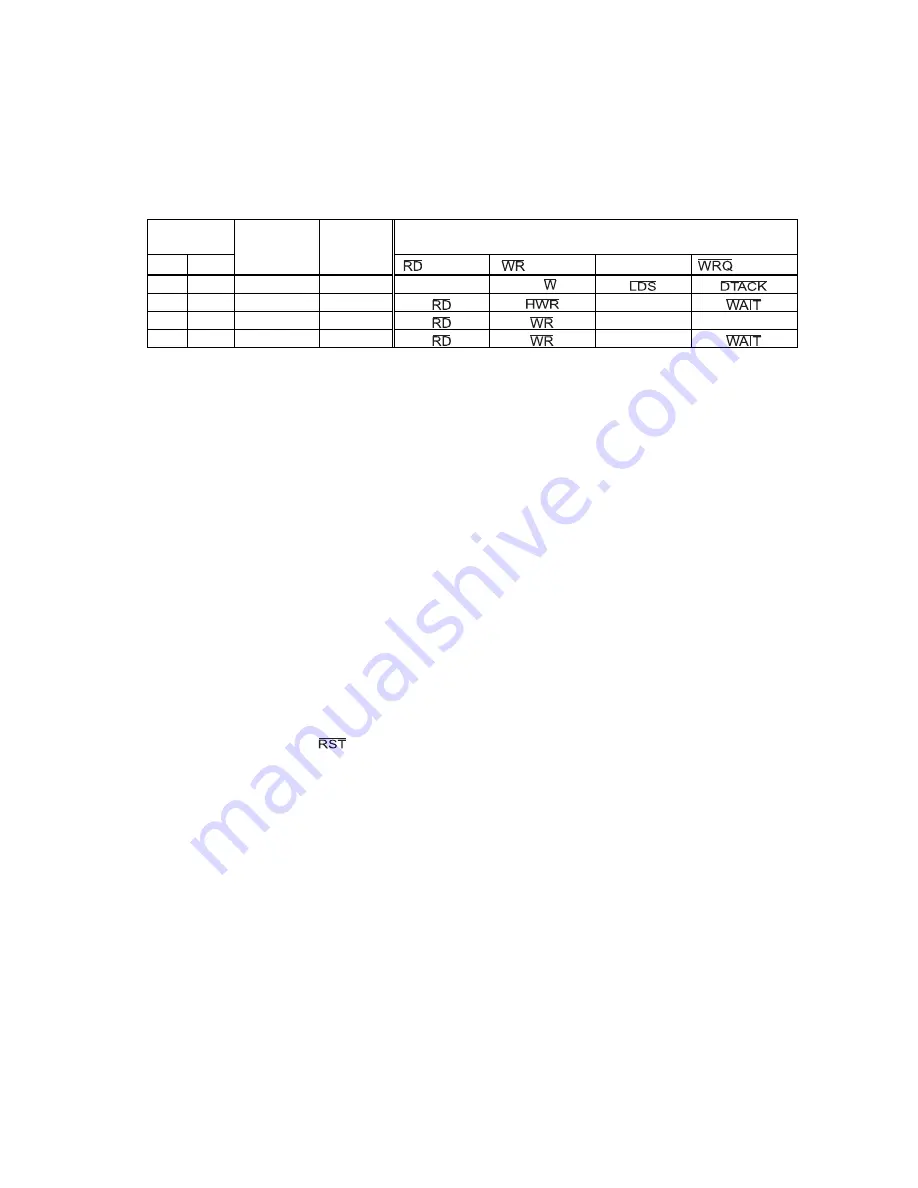

[Example

of

connections

for

CPU

signals]

Setting

status

CPU

signal

to

connect

to

the

6045A

terminals

IF1

IF0

Interface

Name

CPU

type

terminal

terminal

A0

terminal

terminal

L

L

16-bit

I/F-1

68000

+3.3V

R/

L

H

16-bit

I/F-2

H8

(GND)

H

L

16-bit

I/F-3

8086

(GND)

READY

H

H

8-bit

I/F

Z80

A0

16-bit

I/F-1:

A

16-bit

interface

with

a

R/W

mode

input,

strobe

input,

and

acknowledge

output.

The

lower

addresses

correspond

to

the

upper

word

in

the

I/O

buffer.

Convenient

for

use

with

VME

bus

and

68000

series

CPUs.

16-bit

I/F-2:

A

16-bit

interface

with

an

RD

input

and

a

WR

input.

The

lower

addresses

correspond

to

the

upper

word

in

the

I/O

buffer.

Convenient

for

H8

series

CPUs.

16-bit

I/F-3:

A

16-bit

interface

with

an

RD

input

and

a

WR

input.

The

lower

addresses

correspond

to

the

lower

word

in

the

I/O

buffer.

Convenient

for

use

with

8086

series

CPUs.

8-bit

I/F:

An

8-bit

interface

with

an

RD

input

and

a

WR

input.

The

lower

addresses

correspond

to

the

lower

word

in

the

I/O

buffer.

Convenient

for

use

with

Z80

series

CPUs.

6-2.

Hardware

design

precautions

•

All

of

the

input

terminals

can

handle

0

to

+5

V

signal

levels.

•

Although

all

of

the

output

terminals

can

be

pulled

up

to

+5

V

(through

5k

ohms

or

more),

the

output

current

can

not

be

increased

above

that

available

at

3.3

V.

•

To

reset

the

LSI,

hold

the

signal

LOW,

and

input

the

CLK

signal

for

at

least

8-clock

cycles.

•

Any

unused

terminals

from

P0

to

P7

should

be

pulled

down

to

GND

externally.

(5k

to

10k

ohms)

•

When

connecting

a

CPU

with

an

8-bit

bus,

pull

down

terminals

D8

to

D15

to

GND

using

an

external

resistor

(5

k

to

10

k-ohm).

(Shared

use

of

one

resister

for

the

8

lines

is

available.)

•

Use

the

ELL

terminal

to

change

the

±EL

signal

input

logic.

Содержание PCL6113

Страница 1: ...User s Manual For PCL6113 6123 6143 Pulse Control LSI Nippon Pulse Motor Co Ltd...

Страница 11: ...5 3 Terminal Assignment Diagram 3 1 PCL6113 3 2 PCL6123...

Страница 20: ...14 5 Block Diagram...

Страница 115: ...109 11 Stop timing by error...

Страница 116: ...110 13 External Dimensions 13 1 PCL6113...

Страница 117: ...111 13 2 PCL6123...

Страница 118: ...112 13 3 PCL6143...