-

40

-

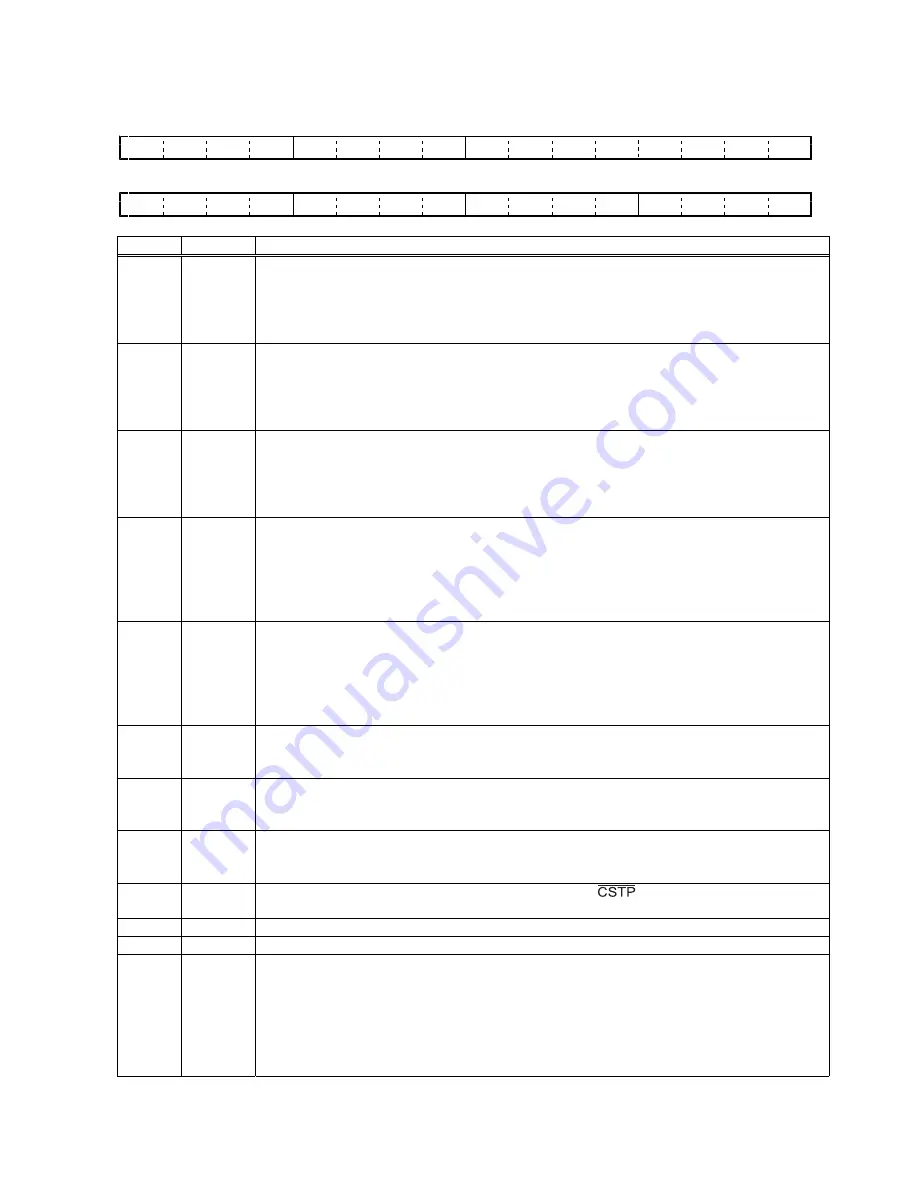

8-3-13.

RENV2

register

This

is

a

register

for

the

Environment

2

settings.

Specify

the

function

of

the

general-purpose

port,

EA/EB

input,

and

PA/PB

input.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

POFF

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

EOFF CSP0 P7M0 P6M0

P4M1

P5M0

P4M0 P3M1 P3M0 P2M1 P2M0 P1M1 P1M0 P0M1 P0M0

0

IEND ORM EZL

EZD3 EZD2 EZD1 EZD0 PDIR PINF PIM1 PIM0 EDIR EINF EIM1 EIM0

Bits

Bit

name

Description

0

to

1 P0M0

to

1 Specify

the

operation

of

the

P0/FUP

terminals

00:

General-purpose

input

01:

General-purpose

output

10:

Output

the

FUP

(acceleration)

signal.

11:

Output

the

FUP

(acceleration)

signal.

2

to

3 P1M0

to

1 Specify

the

operation

of

the

P1/FDW

terminals

00:

General-purpose

input

01:

General-purpose

output

10:

Output

the

FDW

(deceleration)

signal

with

negative

logic.

11:

Output

the

FDW

(deceleration)

signal

with

positive

logic.

4

to

5 P2M0

to

1 Specify

the

operation

of

the

P2/MVC

terminal.

00:

General-purpose

input

01:

General-purpose

output

10:

Output

the

MVC

(low

speed

feeding)

signal

with

negative

logic.

11:

Output

the

MVC

(low

speed

feeding)

signal

with

positive

logic.

6

to

7 P3M0

to

1 Specify

the

operation

of

the

P3/CP1

terminals.

00:

General-purpose

input

01:

General-purpose

output

10:

Output

the

CP1

(satisfied

the

Comparator

1

conditions)

signal

with

negative

logic.

11:

Output

the

CP1

(satisfied

the

Comparator

1

conditions)

signal

with

positive

logic.

8

to

9 P4M0

to

1 Specify

the

operation

of

the

P4/CP2

terminals.

00:

General-purpose

input

01:

General-purpose

output

10:

Output

the

CP2

(satisfied

the

Comparator

2

conditions)

signal

with

negative

logic.

11:

Output

the

CP2

(satisfied

the

Comparator

2

conditions)

signal

with

positive

logic.

10

P5M

Specify

the

operation

of

the

P5

terminals.

0:

General-purpose

input

1:

General-purpose

output

11

P6M

Specify

the

operation

of

the

P6

terminals.

0:

General-purpose

input

1:

General-purpose

output.

12

P7M

Specify

the

operation

of

the

P7

terminals.

0:

General-purpose

input

1:

General-purpose

output

13

CSPO

1:

When

the

RMD/MSP0

=

1,

the

PCL

will

output

a

when

stopped

with

a

command.

14

EOFF

1:

Disables

EA/EB

input.

(Also

disables

input

error

detection.)

15

POFF

1:

Disables

PA/PB

input.

(Also

disables

input

error

detection.)

16

to

17 EIM0

to

1 Specify

the

EA/EB

input

operation.

00:

Multiply

a

90

o

phase

difference

by

1

(Count

up

when

the

EA

input

phase

is

ahead.)

01:

Multiply

a

90

o

phase

difference

by

2

(Count

up

when

the

EA

input

phase

is

ahead.)

10:

Multiply

a

90

o

phase

difference

by

4

(Count

up

when

EA

input

phase

is

ahead.)

11:

Count

up

when

the

EA

signal

rises,

count

down

when

the

EB

signal

falls.

Содержание PCL6113

Страница 1: ...User s Manual For PCL6113 6123 6143 Pulse Control LSI Nippon Pulse Motor Co Ltd...

Страница 11: ...5 3 Terminal Assignment Diagram 3 1 PCL6113 3 2 PCL6123...

Страница 20: ...14 5 Block Diagram...

Страница 115: ...109 11 Stop timing by error...

Страница 116: ...110 13 External Dimensions 13 1 PCL6113...

Страница 117: ...111 13 2 PCL6123...

Страница 118: ...112 13 3 PCL6143...