CACHE AND ON-CHIP DATA RAM

4-7

4

4.5.2

Multi-Word Data Accesses that Partially Hit the Data Cache

The following applies only when data caching is enabled for an access.

For a multi-word load access (

ldl

,

ldt

,

ldq

) in which none of the requested words hit the data cache,

an external bus transaction is started to acquire all the words of the access.

For a multi-word load access that partially hits the data cache, the processor may either:

•

Load or reload all words of the access (even those that hit) from the external bus

•

Load only missing words from the external bus and interleave them with words found in the data cache

The multi-word alignment determines which of the above methods is used:

•

Naturally aligned multi-word accesses cause all words to be reloaded

•

An unaligned multi-word access causes only missing words to be loaded

When any words accessed by a

ldl

,

ldt

, or

ldq

instruction miss the data cache, every word accessed

by that load instruction is updated in the cache.

In each case, the external bus accesses used to acquire the data may consist of none, one, or several

burst accesses based on the alignment of the data and the bus-width of the memory region that

contains the data. See

CHAPTER 14, EXTERNAL BUS

for more details.

A multi-word load access that completely hits in the data cache does not cause external bus accesses.

For a multi-word store access (

stl

,

stt

,

stq

) an external bus transaction is started to write all words

of the access regardless when any or all words of the access hit the data cache. External bus

accesses used to write the data may consist of either one or several burst accesses based on data

alignment and the bus-width of the memory region that receives the data. (See

CHAPTER 14,

EXTERNAL BUS

for more details.) The cache is also updated accordingly as described earlier in

this chapter.

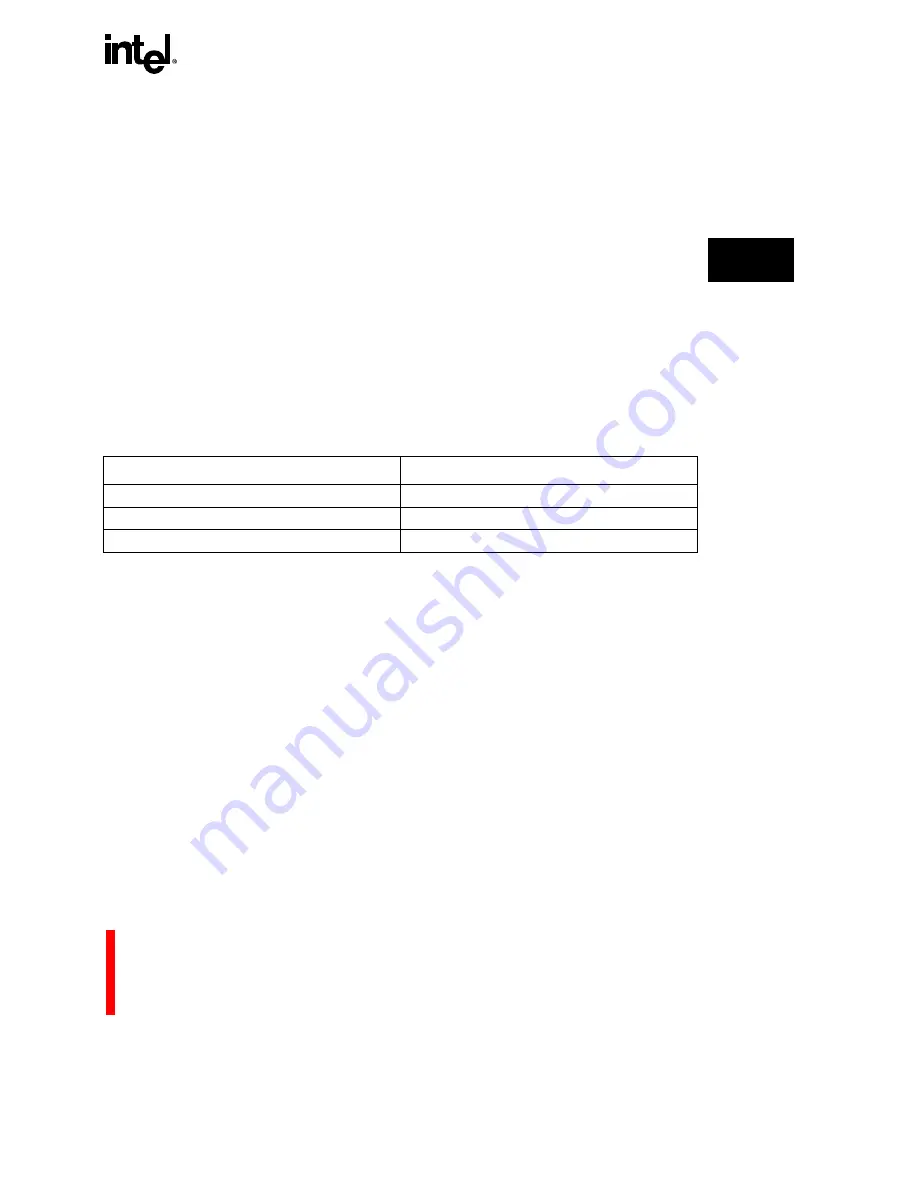

Table 4.1.

Load Instruction

Number of Updated Words

ldq

4 words

ldt

3 words

ldl

2 words

Содержание i960 Jx

Страница 1: ...Release Date December 1997 Order Number 272483 002 i960 Jx Microprocessor Developer s Manual ...

Страница 24: ......

Страница 25: ...1 INTRODUCTION ...

Страница 26: ......

Страница 35: ...2 DATA TYPES AND MEMORY ADDRESSING MODES ...

Страница 36: ......

Страница 46: ......

Страница 47: ...3 PROGRAMMING ENVIRONMENT ...

Страница 48: ......

Страница 73: ...4 CACHE AND ON CHIP DATA RAM ...

Страница 74: ......

Страница 85: ...5 INSTRUCTION SET OVERVIEW ...

Страница 86: ......

Страница 111: ...6 INSTRUCTION SET REFERENCE ...

Страница 112: ......

Страница 195: ...INSTRUCTION SET REFERENCE 6 83 6 Opcode mov 5CCH REG movl 5DCH REG movt 5ECH REG movq 5FCH REG See Also LOAD STORE lda ...

Страница 233: ...7 PROCEDURE CALLS ...

Страница 234: ......

Страница 256: ......

Страница 257: ...8 FAULTS ...

Страница 258: ......

Страница 291: ...9 TRACING AND DEBUGGING ...

Страница 292: ......

Страница 309: ...10 TIMERS ...

Страница 310: ......

Страница 324: ......

Страница 325: ...11 INTERRUPTS ...

Страница 326: ......

Страница 369: ...12 INITIALIZATION AND SYSTEM REQUIREMENTS ...

Страница 370: ......

Страница 412: ......

Страница 413: ...13 MEMORY CONFIGURATION ...

Страница 414: ......

Страница 429: ...14 EXTERNAL BUS ...

Страница 430: ......

Страница 468: ......

Страница 469: ...15 TEST FEATURES ...

Страница 470: ......

Страница 493: ...A CONSIDERATIONS FOR WRITING PORTABLE CODE ...

Страница 494: ......

Страница 502: ......

Страница 503: ...B OPCODES AND EXECUTION TIMES ...

Страница 504: ......

Страница 515: ...C MACHINE LEVEL INSTRUCTION FORMATS ...

Страница 516: ......

Страница 523: ...D REGISTER AND DATA STRUCTURES ...

Страница 524: ......

Страница 550: ......

Страница 551: ...GLOSSARY ...

Страница 552: ......

Страница 561: ...INDEX ...

Страница 562: ......

Страница 578: ......