80

F

D E

M E

E

M M E

E

E

F

D

F

3

3

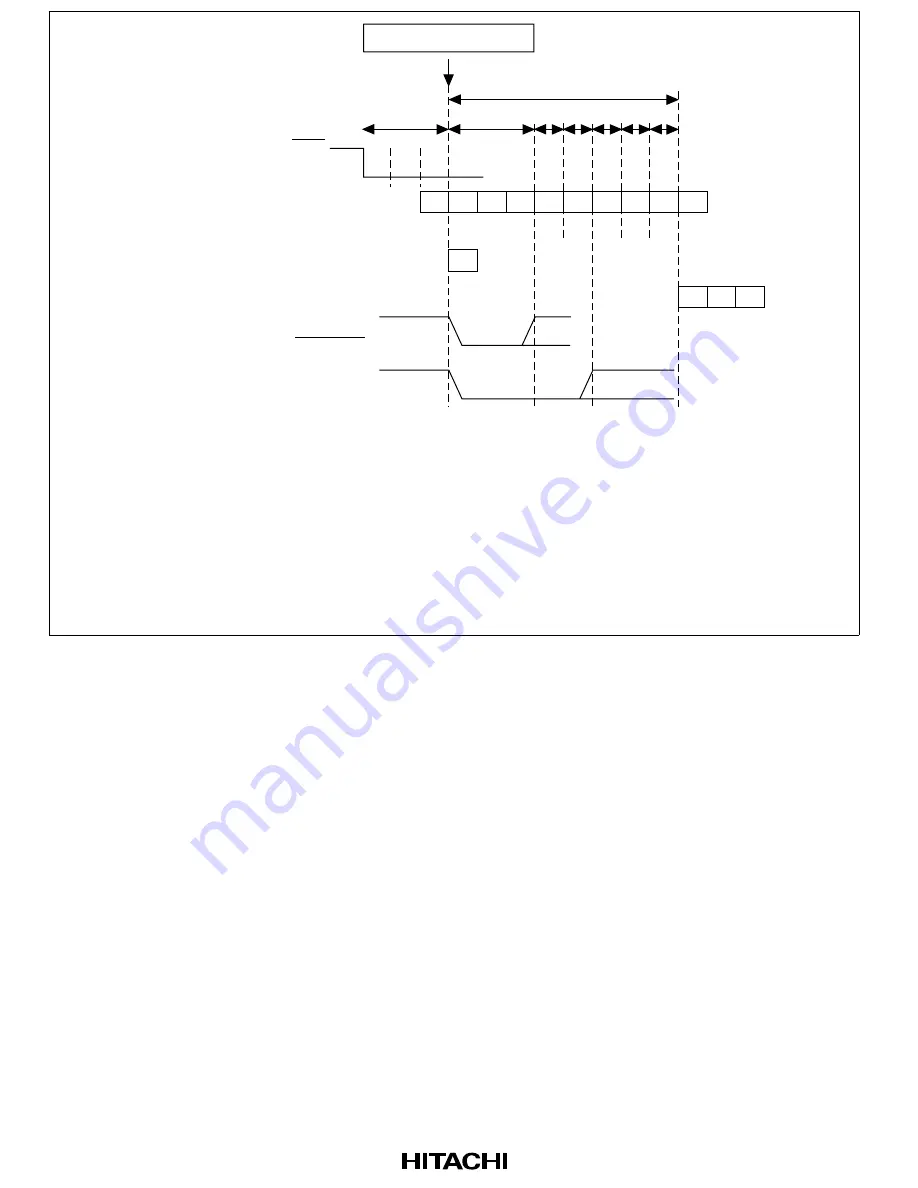

Interrupt accepted

IRQ

m1 m2 1 m3 1

5 + m1 + m2 + m3

Instruction (instruction replaced by

interrupt exception handling)

Overrun fetch

(edge)

(level)

Interrupt service routine—

first instruction

When m1 = m2 = m3, the interrupt response time is 11 cycles.

F (Instruction fetch)

Instruction fetched from memory where program is stored.

D (Instruction decoding)

The fetched instruction is decoded.

E (Instruction execution)

Data operations and address calculations are performed

according to the decoded results.

M (Memory access)

Data in memory is accessed.

Note: For the interrupt acceptance timing, see table 4.1, Exception Source Detection and

Start of Handling, in section 4.1.2, Exception Handling Operation.

IRQOUT

Figure 5.4 Example of Pipelining in IRQ Interrupt Acceptance

5.6

Usage Notes

When the following operations are performed in the order shown when a pin to which IRQ input is

assigned is designated as a general input pin by the pin function controller (PFC) and inputs a low-

level signal, the IRQ falling edge is detected, and an interrupt request is detected, immediately

after the setting in (b) is performed:

•

An interrupt control register (ICR) setting is made so that an interrupt is detected at the falling

edge of IRQ.

…(a)

•

The function of pins to which IRQ input is assigned is switched from general input to IRQ

input by a pin function controller (PFC) setting.

…(b)

Therefore, when switching the pin function from general input pin to IRQ input, the pin function

controller (PFC) setting should be changed to IRQ input while the pin to which IRQ input is

assigned is high.

Содержание HD6417032

Страница 21: ......

Страница 35: ...xiv ...

Страница 85: ...50 ...

Страница 101: ...66 ...

Страница 129: ...94 ...

Страница 135: ...100 ...

Страница 343: ...308 ...

Страница 369: ...334 ...

Страница 383: ...348 ...

Страница 475: ...440 ...

Страница 525: ...490 CK RAS CAS TRp TRc TRcc tRASD1 tRASD2 tCASD3 tCASD2 TRr tCSR Figure 20 18 Self Refresh ...

Страница 578: ...543 CK RAS CAS TRp TRc TRcc tRASD1 tRASD2 tCASD3 tCASD2 TRr tCSR Figure 20 62 Self Refresh ...

Страница 689: ...654 ...