The following example explains the A/D conversion process in single mode when channel 1 (AN1)

is selected and the external trigger is disabled. Figure 9-2 shows the corresponding timing chart.

(1) Software clears the ADST bit to “0,” then selects the single mode (SCAN = “0”) and channel 1

(CH2 to CH0 = “001”), enables the A/D interrupt request (ADIE = “1”), and sets the ADST bit

to “1” to start A/D conversion.

Coding Example: (when using the slow clock, CKS = “0”)

BCLR #5, @H'FFE8

;Clear ADST

MOV.B #H'7F, ROL

MOV.B ROL, @H'FFEA

;Disable external trigger

MOV.B #H'61, ROL

MOV.B ROL, @H'FFE8

;Select mode and channel and set ADST to “1”

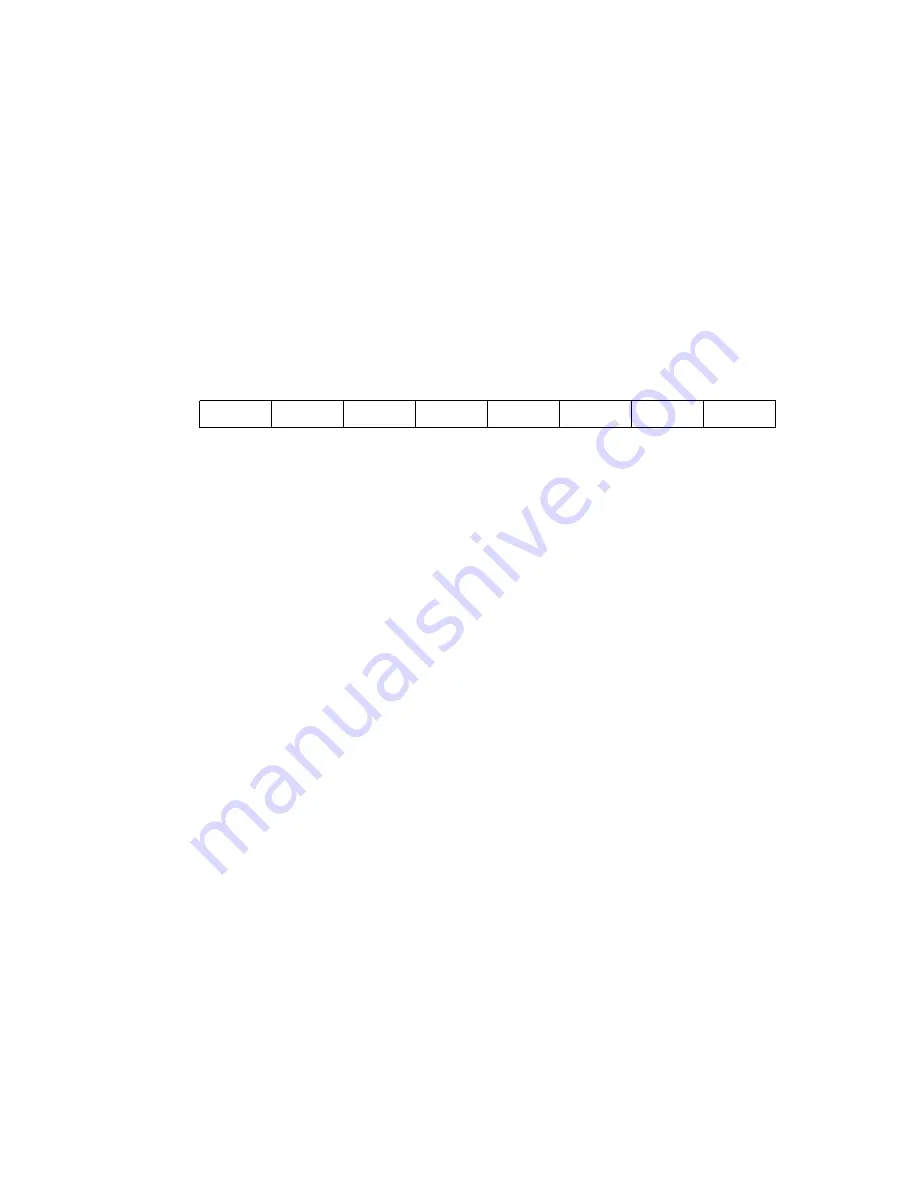

Value set in ADCSR:

ADF

ADIE

ADST

SCAN

CKS

CH2

CH1

CH0

0

1

1

0

0

0

0

1

(2) The A/D converter converts the voltage level at the AN

1

input pin to a digital value. At the end

of the conversion process the A/D converter transfers the result to register ADDRB, sets the

ADF bit to “1,” clears the ADST bit to “0,” and halts.

(3) ADF = “1” and ADIE = “1,” so an A/D interrupt is requested.

(4) The user-coded A/D interrupt-handling routine is started.

(5) The interrupt-handling routine reads the ADCSR value, then writes a “0” in the ADF bit to

clear this bit to “0.”

(6) The interrupt-handling routine reads ADDRB and processes the A/D conversion result.

(7) The routine ends.

Steps (2) to (7) can now be repeated by setting the ADST bit to “1” again.

217

Содержание H8/326 Series

Страница 67: ...58 ...

Страница 121: ...112 ...

Страница 274: ... 3 Clock Settling Timing Ø VCC RES STBY tOSC1 tOSC1 Figure 14 8 Clock Setting Timing 265 ...

Страница 279: ...270 ...