IDT PCI to PCI Bridge and Proprietary Port Specific Registers

PES48T12G2 User Manual

15 - 52

April 5, 2013

Multicast Extended Capability

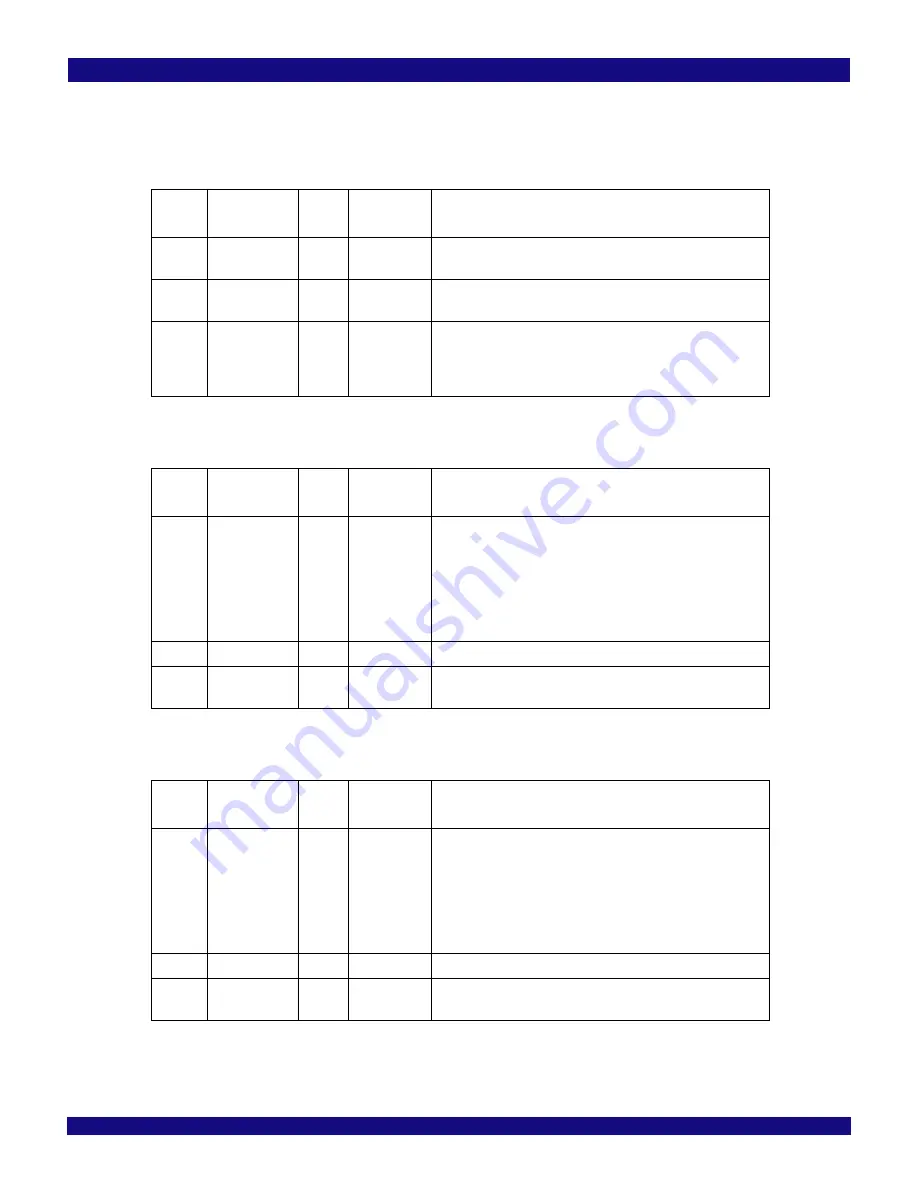

MCCAPH - Multicast Enhanced Capability Header (0x330)

MCCAP - Multicast Capability (0x334)

MCCTL- Multicast Control (0x336)

Bit

Field

Field

Name

Type

Default

Value

Description

15:0

CAPID

RO

0x12

Capability ID.

The value of 0x12 indicates a multicast capability

structure.

19:16

CAPVER

RO

0x1

Capability Version.

The value of 0x1 indicates compatibility with

the PCI-SIG Multicast ECN.

31:20

NXTPTR

RWL

Refer to sec-

Next Pointer.

Next capability pointer. The value of 0x0 terminates

the list.

Bit

Field

Field

Name

Type

Default

Value

Description

5:0

MAXGROUP

RWL

0x1F

Max Multicast Groups

. This field indicates the default number of

multicast groups supported by the switch partition, which is 32.

The maximum number of supported groups is 64, and this field

may be re-programmed during initial switch configuration (e.g., via

EEPROM) to 0x3F to enable support for 64 multicast groups.

The number of supported groups is equal to the value in this field

plus one.

14:6

Reserved

RO

0x0

Reserved field.

15

ECRCREG

RWL

0x1

ECRC Regeneration Supported.

This bit is set to indicate that the

switch supports multicast ECRC regeneration.

Bit

Field

Field

Name

Type

Default

Value

Description

5:0

NUMGROUP

RW

0x0

Number of Multicast Groups.

When the Multicast Enabler (MEN)

bit is set, this field indicates the number of multicast groups that

are enabled.

The number of groups enabled is equal to the value in this field

plus one.

The behavior is undefined when the value in this field exceeds the

value of the MAXGROUP field in the MCCAP register.

14:6

Reserved

RO

0x0

Reserved field.

15

MEN

RW

0x0

Multicast Enable.

When this bit is set, multicast is enabled in the

corresponding switch.

Summary of Contents for 89HPES48T12G2

Page 14: ...IDT Table of Contents PES48T12G2 User Manual vi April 5 2013 Notes...

Page 22: ...IDT Register List PES48T12G2 User Manual xiv April 5 2013 Notes...

Page 38: ...IDT PES48T12G2 Device Overview PES48T12G2 User Manual 1 16 April 5 2013 Notes...

Page 64: ...IDT Reset and Initialization PES48T12G2 User Manual 5 8 April 5 2013 Notes...

Page 82: ...IDT Link Operation PES48T12G2 User Manual 6 18 April 5 2013 Notes...

Page 98: ...IDT SerDes PES48T12G2 User Manual 7 16 April 5 2013 Notes...

Page 118: ...IDT Theory of Operation PES48T12G2 User Manual 8 20 April 5 2013 Notes...

Page 152: ...IDT SMBus Interfaces PES48T12G2 User Manual 12 20 April 5 2013 Notes...

Page 158: ...IDT Multicast PES48T12G2 User Manual 13 6 April 5 2013 Notes...