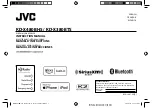

÷M

CLKOUT

CDIV_CLKIN

MCLK

BCLK

DIN

GPIO

MISO

DOUT

PLL_CLK

DAC_CLK

ADC_CLK

DAC_MOD_CLK

DIG_MIC_CLK

M = 1,2,...,127,128

Clock Generation and PLL

In the mode when TLV320DAC3203 is configured to drive the BCLK pin (Page 0, Register 27, D3=’1’) it

can be driven as divided value of BDIV_CLKIN. The division value can be programmed in Page 0,

Register 30, D(6:0) from 1 to 128. The BDIV_CLKIN can itself be configured to be one of DAC_CLK,

DAC_MOD_CLK, ADC_CLK or DIG_MIC_CLK by configuring the BDIV_CLKIN mux in Page 0, Register

29, D(1:0). Additionally a general purpose clock can be driven out on either GPIO, DOUT or MISO pin.

This clock can be a divided down version of CDIV_CLKIN. The value of this clock divider can be

programmed from 1 to 128 by writing to Page 0, Register 26, D(6:0). The CDIV_CLKIN can itself be

programmed as one of the clocks among the list shown in

. This can be controlled by

programming the mux in Page 0, Register 25, D(2:0).

Figure 2-47. General Purpose Clock Output Options

Table 2-21. Maximum TLV320DAC3203 Clock Frequencies

DVdd

≥

1.26V

DVdd

≥

1.65V

CODEC_CLKIN

50MHz

137MHz when NDAC is even, NADC is even

112MHz when NDAC is even, NADC is odd

110MHz when NDAC is odd, NADC is even

110MHz when NDAC is odd, NADC is odd

ADC_CLK

25MHz

55.296MHz

DIG_MIC_CLK

6.758MHz

6.758MHz

ADC_FS

0.192MHz

0.192MHz

DAC_CLK

25MHz

55.296MHz

DAC_MOD_CLK

6.758MHz

6.758MHz

4.2MHz when Class-D Mode Headphone

is used

DAC_FS

0.192MHz

0.192MHz

BDIV_CLKIN

25MHz

55.296MHz

CDIV_CLKIN

50MHz

112MHz when M is odd

137MHz when M is even

64

TLV320DAC3203 Application

SLAU434 – May 2012

Copyright © 2012, Texas Instruments Incorporated