+

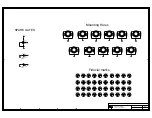

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

+

+

+

D

S

2119M

-R1

-R2

-R3

-R4

-R5

-R6

-R7

-R8

+R1

+R2

+R3

+R4

+R5

+R6

+R7

+R8

+R9

DIFF_CAP

HSGND2

HSGND1

GND

D_SNS

VREF

M_S

ISO

-R9

TPWR1

TPWR0

D

S

2119M

-R1

-R2

-R3

-R4

-R5

-R6

-R7

-R8

+R1

+R2

+R3

+R4

+R5

+R6

+R7

+R8

+R9

DIFF_CAP

HSGND2

HSGND1

GND

D_SNS

VREF

M_S

ISO

-R9

TPWR1

TPWR0

D

S

2119M

-R1

-R2

-R3

-R4

-R5

-R6

-R7

-R8

+R1

+R2

+R3

+R4

+R5

+R6

+R7

+R8

+R9

DIFF_CAP

HSGND2

HSGND1

GND

D_SNS

VREF

M_S

ISO

-R9

TPWR1

TPWR0

up-to-date information regarding implementation of this subsystem

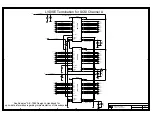

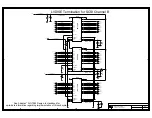

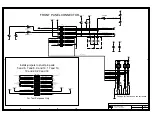

See Adaptec* AIC-7902 Design-In Handbook for

20MIL

LVD/SE Termination for SCSI Channel A

Use 40 mil trace

20 MIL trace

20 MIL trace

20MIL

20 MIL trace

20MIL

3

5

8

10

12

19

21

24

2

4

7

9

11

18

20

23

25

17

22

6

14

16

1

15

13

26

28

27

U95

27

28

26

13

15

1

16

14

6

22

17

25

23

20

18

11

9

7

4

2

24

21

19

12

10

8

5

3

U94

3

5

8

10

12

19

21

24

2

4

7

9

11

18

20

23

25

17

22

6

14

16

1

15

13

26

28

27

U93

LVTRMPWR_A

75,77

R697

4.7K

R

700

1K

C

1384

0.

1U

F

0.

1U

F

C

1383

C

1382

0.

1U

F

0.

1U

F

C

1381

0.

1U

F

C

1380

CHA_TERMEN

73

DIFFSENSEA_R

73,77

12 C

1436

4.

7U

F

2

1

4.

7U

F

C

1435

2

1

10U

F

C

1434

LVSCDAM13

73,77

LVSCDAPHM

73,77

LVSCDAM1

73,77

LVSCDAM14

73,77

R

702

20K

LVSCDAM10

73,77

LVMSGAP

73,77

LVCDAP

73,77

LVIOAP

73,77

LVSCDAP9

73,77

LVSCDAP11

73,77

LVSCDAP10

73,77

LVSCDAP8

73,77

LVREQAP

73,77

LVSELAP

73,77

LVMSGAM

73,77

LVCDAM

73,77

LVIOAM

73,77

LVSCDAM9

73,77

LVSCDAM11

73,77

LVSCDAM8

73,77

LVREQAM

73,77

LVSELAM

73,77

LVSCDAP4

73,77

LVSCDAP6

73,77

LVSCDAPLP

73,77

LVACKAP

73,77

LVRSTAP

73,77

LVBSYAP

73,77

LVATNAP

73,77

LVSCDAP7

73,77

LVSCDAP5

73,77

LVSCDAP12

73,77

LVSCDAP14

73,77

LVSCDAPHP

73,77

LVSCDAP1

73,77

LVSCDAP3

73,77

LVSCDAP2

73,77

LVSCDAP0

73,77

LVSCDAP15

73,77

LVSCDAP13

73,77

LVSCDAM4

73,77

LVSCDAM6

73,77

LVSCDAPLM

73,77

LVACKAM

73,77

LVRSTAM

73,77

LVBSYAM

73,77

LVATNAM

73,77

LVSCDAM7

73,77

LVSCDAM5

73,77

LVSCDAM12

73,77

LVSCDAM3

73,77

LVSCDAM2

73,77

LVSCDAM0

73,77

LVSCDAM15

73,77

2

1

4.

7U

F

C

1437

78

Содержание Xeon

Страница 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Страница 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Страница 34: ...Platform Stack Up and Component Placement Overview 34 Design Guide This page is intentionally left blank ...

Страница 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Страница 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Страница 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Страница 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Страница 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Страница 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Страница 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Страница 222: ...Schematics 222 Design Guide This page is intentionally left blank ...