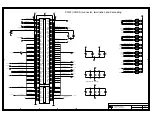

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

+

+

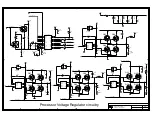

+12V

+5V_A

+5V_B

+5V_C

+5V_D

+5V_E

+5V_F

+5V_G

+5V_H

-12V

3_3VAUX_1

3_3V_A

3_3V_B

3_3V_C

3_3V_D

3_3V_E

3_3V_F

3_3V_G

3_3V_H

3_3V_I

3_3V_M

3_3V_N

3_3V_O

3_3V_P

3_3V_Q

3_3V_R

3_3V_S

3_3V_T

ACK64_N

AD0

AD1

AD10

AD11

AD12

AD13

AD14

AD15

AD16

AD17

AD18

AD19

AD2

AD20

AD21

AD22

AD23

AD24

AD25

AD26

AD27

AD28

AD29

AD3

AD30

AD31

AD4

AD5

AD6

AD7

AD8

AD9

CBE0_N

CBE1_N

CBE2_N

CBE3_N

CLK

DEVSEL_N

FRAME_N

GND_A

GND_AA

GND_B

GND_BB

GND_C

GND_CC

GND_D

GND_E

GND_F

GND_G

GND_H

GND_I

GND_J

GND_S

GND_T

GND_U

GND_V

GND_W

GND_X

GND_Z

GNT_N

IDSEL

INTA_N

INTB_N

INTC_N

INTD_N

IRDY_N

LOCK_N

M66EN

PAR

PCIXCAP

PERR_N

PME_N

PRSNT1_N

PRSNT2_N

REQ64_N

REQ_N

RESV_A

RESV_B

RESV_E

RESV_F

RST_N

SBO_N

SDONE

SERR_N

STOP_N

TCK

TDI

TDO

TMS

TRDY_N

TRST_N

PCI_X_HI_TEST_CONN

KEY

KEY

continued

GND_31A95

GND_0

B95

CLK200_N

CLK200

3_3V_J

3_3V_K

3_3V_L

3_3V_U

3_3V_V

3_3V_W

CLK66

AD32

AD33

AD34

AD35

AD36

AD37

AD38

AD39

AD40

AD41

AD42

AD43

AD44

AD45

AD46

AD47

AD48

AD49

AD50

AD51

AD52

AD53

AD54

AD55

AD56

AD57

AD58

AD59

AD60

AD61

AD62

AD63

CBE4_N

CBE5_N

CBE6_N

CBE7_N

GND_10

GND_11

GND_12

GND_13

GND_14

GND_15

GND_16

GND_17

GND_18

GND_19

GND_2

GND_20

GND_21

GND_22

GND_23

GND_24

GND_25

GND_26

GND_27

GND_28

GND_29

GND_3

GND_4

GND_5

GND_6

GND_7

GND_8

GND_9

GND_DD

GND_EE

GND_FF

GND_GG

GND_HH

GND_II

GND_JJ

GND_K

GND_KK

GND_L

GND_M

GND_N

GND_O

GND_P

GND_Q

GND_R

HI0

HI1

HI10

HI11

HI12

HI13

HI14

HI15

HI20

HI21

HI2

HI3

HI4

HI5

HI6

HI7

HI8

HI9

HCA_PRES

PSTRBF

PSTRBS

HI19

PAR64

RSVD_7

RSVD_6

HI_RESET_N

RESV_C

RESV_D

RESV_G

RESV_H

RESV_I

HI16

HI17

RSVD_1

USE_CLK200

RSVD_3

RSVD_5

HI18

PUSTRBF

PUSTRBS

PWR_GD

GND_1

GND_30

PCI_X_HI_TEST_CONN

KEY

continued

KEY

HI Test Extension

Place caps near connector

PCI-X 66MHz SLOT D (Hub Interface Extension for Test Purposes Only)

A66

A75

A84

B70

B79

B88

A91

B90

A89

B89

A88

B87

A86

B86

A85

B84

A83

B83

A82

B81

A80

B80

A79

B78

A77

B77

A76

B75

A74

B74

A73

B72

A71

B71

A70

B69

A68

B68

B64

B67

B73

B76

B82

B85

B91

B94

A69

A72

A78

A81

A87

A90

A93

A67

A92

A94

B63

B92

B93

B65

B66

A64

A65

A63

B101

B96

B97

B98

B99

B100

B102

B103

B104

B105

B106

B107

B108

B109

B110

B111

B112

B113

B114

B115

B116

B117

B118

B119

B120

B121

B122

B123

B124

B125

B126

B127

B128

B129

A129

A128

A127

A126

A125

A124

A123

A122

A121

A120

A119

A118

A117

A116

A115

A114

A113

A112

A111

A110

A109

A108

A107

A106

A105

A104

A103

A102

A101

A100

A99

A98

A97

A96

J12

A2

A5

A8

A61

A62

B5

B6

B61

B62

B1

A14

A10

A16

A21

A27

A33

A39

A45

A53

A59

B19

B25

B31

B36

B41

B43

B54

B59

B60

A58

B58

B48

A47

B47

A46

B45

A44

A32

B32

A31

B30

A57

A29

B29

A28

B27

A25

B24

A23

B23

A22

B21

B56

A20

B20

A55

B55

A54

B53

B52

A49

A52

B44

B33

B26

B16

B37

A34

A18

B50

A24

B51

A30

B57

A35

A37

A42

A48

A50

A51

A56

B3

B15

B17

B22

B28

B34

B46

A17

A26

A6

B7

A7

B8

B35

B39

B49

A43

B38

B40

A19

B9

B11

A60

B18

A9

A11

B10

B14

A15

A41

A40

B42

A38

B2

A4

B4

A3

A36

A1

J12

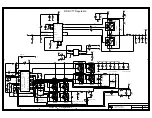

SLOT_D_PSTRBS

11

SLOT_D_HI20

11

SLOT_D_HI15

SLOT_D_HI[15:0]

11,52

SLOT_D_HI2

SLOT_D_HI6

SLOT_D_HI9

SLOT_D_HI4

SLOT_D_HI13

SLOT_D_HI11

SLOT_D_HI0

SLOT_D_PUSTRBS

11

SLOT_D_HI16

11

SLOT_D_PUSTRBF

11

SLOT_D_HI14

SLOT_D_HI[15:0]

11,52

SLOT_D_HI1

SLOT_D_HI12

SLOT_D_HI10

SLOT_D_HI8

SLOT_D_HI7

SLOT_D_HI5

SLOT_D_HI3

SLOT_D_HI21

11

SLOT_D_HI17

11

SLOT_D_HI18

11

52

SLOT_D_HI_PRES_N

41

SLOT_D_SMDAT

45

SLOT_D_SMCLK

45

SLOT_D_3V

41,46,52

12

C

694

22U

F

2

1

22U

F

C

695

22U

F

C

692

C

693

22U

F

SLOT_D_PSTRBF

11

100

R350

1K

R

352

C

436

0.

1U

F

0.

1U

F

C

435

C

434

0.

1U

F

0.

1U

F

C

433

0.

1U

F

C

432

C

431

0.

1U

F

0.

1U

F

C

430

C

429

0.

1U

F

0.

01U

F

C

1659

1

8

3

4

5

6

7

2

RP196

18K

PCIRST_2_N

29,33,53

41,46,52

SLOT_D_3V

52

SLOT_D_TDI

52

SLOT_D_TMS

52

SLOT_D_TMS

52

SLOT_D_TDI

SLOT_D_AD22

46,52

SLOT_D_AD22

SLOT_D_AD[63:0]

46,52

SLOT_D_AD30

SLOT_D_AD0

SLOT_D_AD2

SLOT_D_AD4

SLOT_D_AD6

SLOT_D_AD9

SLOT_D_AD11

SLOT_D_AD13

SLOT_D_AD15

SLOT_D_AD16

SLOT_D_AD18

SLOT_D_AD20

SLOT_D_AD24

SLOT_D_AD26

SLOT_D_AD28

SLOT_D_CLK66

65

41,52

SLOT_D_M12V

SLOT_D_3V

41,46,52

SLOT_D_5V

41,52

SLOT_D_AD60

SLOT_D_AD58

SLOT_D_AD56

SLOT_D_AD54

SLOT_D_AD52

SLOT_D_AD50

SLOT_D_AD48

SLOT_D_AD46

SLOT_D_AD44

SLOT_D_AD42

SLOT_D_AD40

SLOT_D_AD38

SLOT_D_AD36

SLOT_D_AD34

SLOT_D_AD32

SLOT_D_AD62

SLOT_D_AD[63:0]

46,52

SLOT_D_AD61

SLOT_D_AD59

SLOT_D_AD57

SLOT_D_AD55

SLOT_D_AD53

SLOT_D_AD51

SLOT_D_AD49

SLOT_D_AD47

SLOT_D_AD45

SLOT_D_AD43

SLOT_D_AD41

SLOT_D_AD39

SLOT_D_AD37

SLOT_D_AD35

SLOT_D_AD33

SLOT_D_AD63

SLOT_D_AD[63:0]

46,52

SLOT_D_5V

41,52

38,52

SLOT_D_PCIXCAP

SLOT_D_CBE5_N

46

SLOT_D_CBE7_N

46

SLOT_D_PAR64

46

SLOT_D_CBE4_N

46

SLOT_D_CBE6_N

46

SLOT_D_CBE3_N

46

SLOT_D_AD31

SLOT_D_AD[63:0]

46,52

SLOT_D_AD1

SLOT_D_AD3

SLOT_D_AD5

SLOT_D_AD7

SLOT_D_AD8

SLOT_D_AD10

SLOT_D_AD12

SLOT_D_AD14

SLOT_D_AD17

SLOT_D_AD19

SLOT_D_AD21

SLOT_D_AD23

SLOT_D_AD25

SLOT_D_AD27

SLOT_D_AD29

SLOT_D_CBE2_N

46

SLOT_D_IRDY_N

46

SLOT_D_DEVSEL_N

46

SLOT_D_PCIXCAP

38,52

SLOT_D_PLOCK_N

46

SLOT_D_PERR_N

46

SLOT_D_SERR_N

46

SLOT_D_CBE1_N

46

SLOT_D_M66EN

38,52

SLOT_D_CBE0_N

46

SLOT_D_PAR

46

SLOT_D_STOP_N

46

SLOT_D_TRDY_N

46

SLOT_D_FRAME_N

46

SLOT_D_REQ_N

46

SLOT_D_GNT_N

46

SLOT_D_RESET_N

38

SLOT_D_INTC_N

46

SLOT_D_INTA_N

46

SLOT_D_12V

41,52

SLOT_D_PCLK

43

SLOT_D_INTB_N

46

SLOT_D_INTD_N

46

SLOT_D_M12V

41,52

SLOT_D_IDSEL

SLOT_D_ACK64_N

46

SLOT_D_REQ64_N

46

38,52

SLOT_D_M66EN

PCI_SLOTS_TCK

47-51,57

PCI_SLOTS_TRST_N

47-51,57

C

1660

0.

01U

F

SLOT_D_PRSNT1

38

SLOT_D_PRSNT2

38

41,52

SLOT_D_12V

Содержание Xeon

Страница 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Страница 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Страница 34: ...Platform Stack Up and Component Placement Overview 34 Design Guide This page is intentionally left blank ...

Страница 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Страница 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Страница 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Страница 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Страница 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Страница 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Страница 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Страница 222: ...Schematics 222 Design Guide This page is intentionally left blank ...