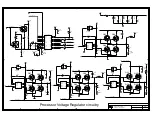

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

+

V

3_3

LD

A

L

T

ID

B

LD

A

L

T

ID

A

W

ID

EPSB

W

ID

EPSA

ST

PW

C

T

L

B

ST

PW

C

T

L

A

LE

D

B

LE

D

A

PC

IR

ST

O

U

T

R

SVD

1

2

R

SVD

1

1

L

V

R

EXT

2

L

V

R

EXT

1

IO

B

M

RE

Q

B

M

CDB

M

SEL

BM

MS

G

B

M

R

ESET

BM

AT

N

B

M

AC

KBM

BSYBM

SC

D

BPL

M

S

CDB

M

1

S

CDB

M

2

S

CDB

M

3

S

CDB

M

4

S

CDB

M

5

S

CDB

M

6

S

CDB

M

7

S

CDB

M

8

S

CDB

M

9

S

CDB

M

1

0

S

CDB

M

1

1

S

CDB

M

1

2

S

CDB

M

1

3

S

CDB

M

1

4

S

CDB

M

1

5

IO

A

M

RE

Q

A

M

CDA

M

SEL

AM

MS

G

A

M

R

ESET

AM

AC

KAM

BSYAM

AT

N

A

M

SC

D

APL

M

SC

D

APH

M

S

CDA

M

0

S

CDA

M

1

S

CDA

M

2

S

CDA

M

3

S

CDA

M

5

S

CDA

M

6

S

CDA

M

7

S

CDA

M

8

S

CDA

M

9

S

CDA

M

1

0

S

CDA

M

1

1

S

CDA

M

1

2

S

CDA

M

1

3

S

CDA

M

1

4

S

CDA

M

1

5

SC

L

K

IN

M

SC

L

K

IN

P

IDDA

T

B

IDDA

T

A

EXPAC

T

B

EXPAC

T

A

R

SVD

9

R

SVD

1

0

PR

ST

D

IF

F

SEN

SEB

D

IF

F

SEN

SEA

IO

B

P

RE

Q

B

P

CDB

P

SEL

BP

MS

G

B

P

R

ESET

BP

AT

N

B

P

AC

KBP

SC

D

BPL

P

SC

D

BPH

P

SC

D

BP0

SC

D

BP2

SC

D

BP3

SC

D

BP4

SC

D

BP5

SC

D

BP6

SC

D

BP7

SC

D

BP8

SC

D

BP9

SC

D

BP1

0

SC

D

BP1

3

SC

D

BP1

4

SC

D

BP1

5

IO

A

P

RE

Q

A

P

CDA

P

SEL

AP

MS

G

A

P

R

ESET

AP

AC

KAP

BSYAP

AT

N

A

P

SC

D

APL

P

SC

D

APH

P

SC

D

AP0

SC

D

AP1

SC

D

AP2

SC

D

AP3

SC

D

AP4

SC

D

AP5

SC

D

AP6

SC

D

AP7

SC

D

AP8

SC

D

AP9

SC

D

AP1

0

SC

D

AP1

1

SC

D

AP1

2

SC

D

AP1

3

SC

D

AP1

4

SC

D

AP1

5

S

CDA

M

4

SC

D

BP1

2

SC

D

BP1

1

SC

D

BP1

S

CDB

M

0

SC

D

BPH

M

BSYBP

SC

SI

M

isc.

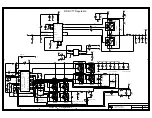

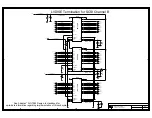

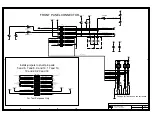

Adaptec* AIC-7902

SCSI Controller

See Adaptec* AIC-7902 Design-In Handbook for

up-to-date information regarding implementation of this subsystem

73

M2

3

M2

5

L23

J2

3

L24

J2

6

L25

K2

6

N2

6

B1

2

B1

3

B9

C9

B4

A3

A2

C1

D1

D3

F2

E2

E4

F4

K3

J4

J2

H4

H2

G4

G2

A5

C5

A6

C6

P3

N2

N4

M3

E2

6

D2

5

C2

5

B2

6

C2

4

A2

5

B2

4

B2

3

D2

2

B2

2

B1

7

B1

8

D1

8

B1

9

D1

9

D2

0

B2

1

D2

1

E2

4

F2

6

F2

4

G25

B1

5

C1

5

C1

6

D1

6

B1

0

B1

1

M2

4

M2

6

K2

4

J2

4

K2

3

J2

5

AD

1

D9

H2

5

C4

B3

B2

B1

C2

D2

F1

E1

F3

L2

K4

J3

J1

H3

H1

G3

G1

B5

D5

B6

N1

M4

M2

E2

5

D2

4

D2

6

C2

6

B2

5

A2

6

A2

4

A2

3

C2

2

A2

2

A1

7

A1

8

C1

8

A1

9

C1

9

A2

0

C2

0

A2

1

C2

1

E2

3

F2

5

F2

3

G24

A1

5

D1

5

B1

6

D1

7

B2

0

N3

D6

K2

L4

L3

E3

U7

8

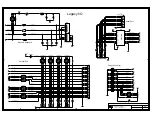

R761

1K

1K

R760

R

681

6.

19K

1%

R

766

10K

10K

R

765

R

680

0

R683

4.7K

R682

4.7K

1

2

3

4

5

6

7

8

RP282

1K

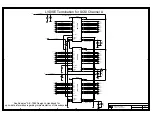

P

64H

2_2_P

A

_

P

C

IR

S

T

_N

31

L

VAT

N

B

M

77,

79

L

VBSYBP

77,

79

L

VSC

D

BPL

P

77,

79

LV

R

S

T

B

P

77,

79

L

VAT

N

B

P

77,

79

L

VBSYAP

77,

78

L

VAC

KAP

77,

78

L

VSC

D

BPH

P

77,

79

L

VSEL

BP

77,

79

LV

M

S

GB

P

77,

79

L

VAC

KBP

77,

79

LV

IO

A

M

77,

78

LV

R

S

T

A

M

77,

78

LV

R

S

T

B

M

77,

79

LV

R

S

T

A

P

77,

78

D

IF

F

SEN

SEB_

R

77,

79

D

IF

F

SEN

SEA_

R

77,

78

LV

IO

B

P

77,

79

D

IF

F

SEN

SEA

D

IF

F

SEN

SEB

R684

4.7K

NOPOP

CHA

_

T

E

R

M

E

N

78

L

VAC

KAM

77,

78

L

V

S

CDB

M

0

77,

79

L

V

S

CDA

M

0

77,

78

L

VSC

D

AP0

77,

78

A

IC_

CL

K

N

M

76

L

VSC

D

BP0

77,

79

LV

IO

A

P

77,

78

L

VSC

D

AP1

77,

78

L

VSC

D

AP2

77,

78

L

VSC

D

AP3

77,

78

L

VSC

D

AP4

77,

78

L

VSC

D

AP5

77,

78

L

VSC

D

AP6

77,

78

L

VSC

D

AP7

77,

78

L

VSC

D

AP8

77,

78

L

VSC

D

AP9

77,

78

L

VSC

D

AP1

0

77,

78

L

VSC

D

AP1

1

77,

78

L

VSC

D

AP1

2

77,

78

L

VSC

D

AP1

3

77,

78

L

VSC

D

AP1

4

77,

78

L

VSC

D

AP1

5

77,

78

L

VSC

D

BP1

77,

79

L

VSC

D

BP2

77,

79

L

VSC

D

BP3

77,

79

L

VSC

D

BP4

77,

79

L

VSC

D

BP5

77,

79

L

VSC

D

BP6

77,

79

L

VSC

D

BP7

77,

79

L

VSC

D

BP8

77,

79

L

VSC

D

BP9

77,

79

L

VSC

D

BP1

0

77,

79

L

VSC

D

BP1

1

77,

79

L

VSC

D

BP1

2

77,

79

L

VSC

D

BP1

3

77,

79

L

VSC

D

BP1

4

77,

79

L

VSC

D

BP1

5

77,

79

LV

R

E

QA

P

77,

78

L

V

CDA

P

77,

78

L

VSEL

AP

77,

78

LV

M

S

GA

P

77,

78

L

VAT

N

A

P

77,

78

L

VSC

D

APL

P

77,

78

L

VSC

D

APH

P

77,

78

LV

R

E

QB

P

77,

79

L

V

CDB

P

77,

79

A

IC_

CL

K

N

P

76

L

V

S

CDA

M

1

77,

78

L

V

S

CDA

M

2

77,

78

L

V

S

CDA

M

3

77,

78

L

V

S

CDA

M

4

77,

78

L

V

S

CDA

M

5

77,

78

L

V

S

CDA

M

6

77,

78

L

V

S

CDA

M

7

77,

78

L

V

S

CDA

M

8

77,

78

L

V

S

CDA

M

9

77,

78

L

V

S

CDA

M

1

0

77,

78

L

V

S

CDA

M

1

1

77,

78

L

V

S

CDA

M

1

2

77,

78

L

V

S

CDA

M

1

3

77,

78

L

V

S

CDA

M

1

4

77,

78

L

V

S

CDA

M

1

5

77,

78

L

V

S

CDB

M

1

77,

79

L

V

S

CDB

M

2

77,

79

L

V

S

CDB

M

3

77,

79

L

V

S

CDB

M

4

77,

79

L

V

S

CDB

M

5

77,

79

L

V

S

CDB

M

6

77,

79

L

V

S

CDB

M

7

77,

79

L

V

S

CDB

M

8

77,

79

L

V

S

CDB

M

9

77,

79

L

V

S

CDB

M

1

0

77,

79

L

V

S

CDB

M

1

1

77,

79

L

V

S

CDB

M

1

2

77,

79

L

V

S

CDB

M

1

3

77,

79

L

V

S

CDB

M

1

4

77,

79

L

V

S

CDB

M

1

5

77,

79

LV

R

E

QA

M

77,

78

L

V

CDA

M

77,

78

L

VSEL

AM

77,

78

LV

M

S

GA

M

77,

78

L

VBSYAM

77,

78

L

VAT

N

A

M

77,

78

L

VSC

D

APL

M

77,

78

L

VSC

D

APH

M

77,

78

LV

IO

B

M

77,

79

LV

R

E

QB

M

77,

79

L

V

CDB

M

77,

79

L

VSEL

BM

77,

79

LV

M

S

GB

M

77,

79

L

VAC

KBM

77,

79

L

VBSYBM

77,

79

L

VSC

D

BPL

M

77,

79

L

VSC

D

BPH

M

77,

79

CHB

_

T

E

R

M

E

N

79

R685

4.7K

NOPOP

Содержание Xeon

Страница 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Страница 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Страница 34: ...Platform Stack Up and Component Placement Overview 34 Design Guide This page is intentionally left blank ...

Страница 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Страница 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Страница 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Страница 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Страница 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Страница 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Страница 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Страница 222: ...Schematics 222 Design Guide This page is intentionally left blank ...