VTT_

D

D

R

+

V

2_5

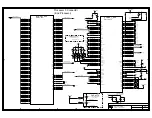

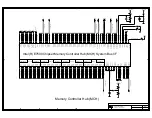

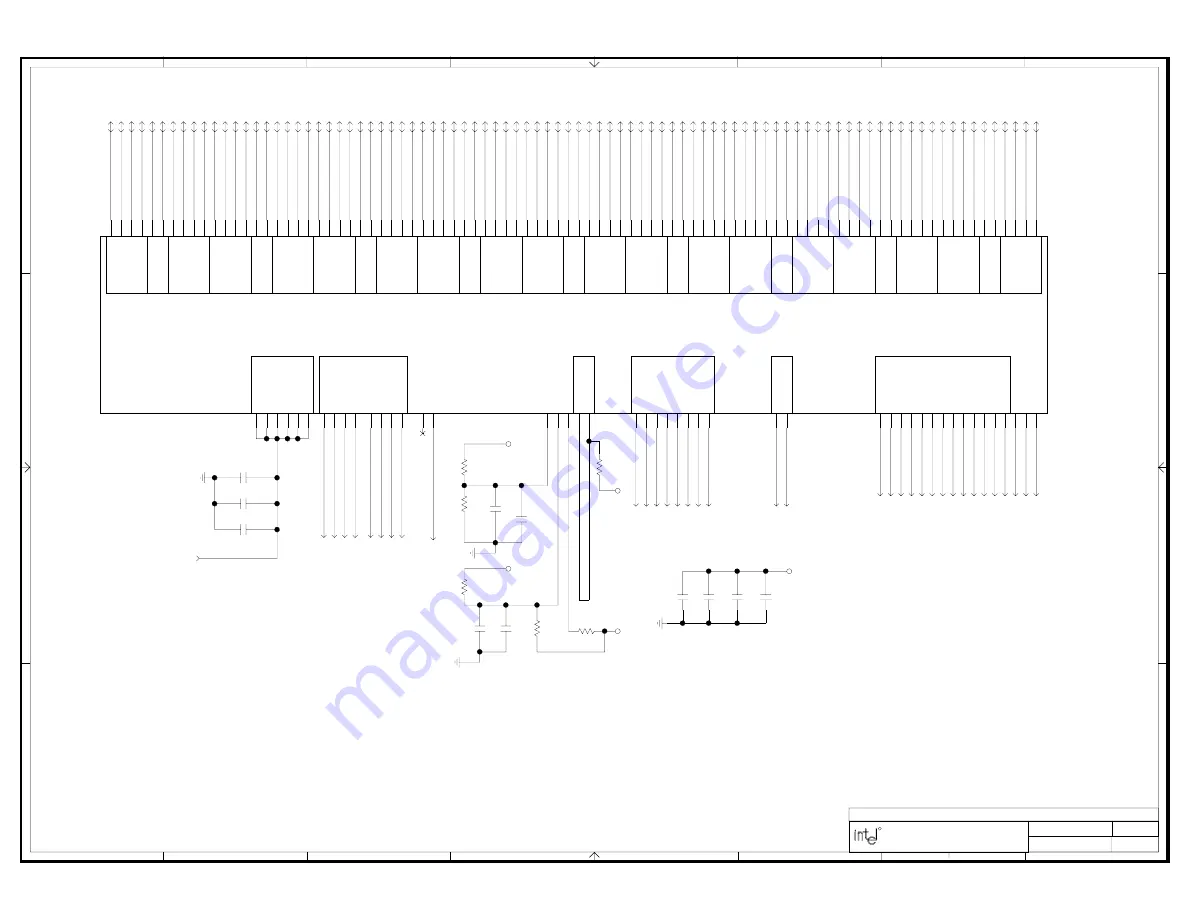

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

VTT_

D

D

R

VTT_

D

D

R

VTT_

D

D

R

DDRCV

O

L

_

A

DDRCV

O

H

_

A

D

Q

13_A

D

Q

16_A

D

Q

17_A

D

Q

18_A

D

Q

19_A

D

Q

22_A

C

B

7_A

D

Q

63_A

D

Q

61_A

D

Q

60_A

D

Q

59_A

D

Q

58_A

D

Q

57_A

D

Q

56_A

D

Q

55_A

D

Q

52_A

D

Q

51_A

D

Q

50_A

D

Q

49_A

D

Q

48_A

D

Q

47_A

D

Q

46_A

D

Q

45_A

D

Q

43_A

D

Q

42_A

D

Q

41_A

D

Q

40_A

D

Q

39_A

D

Q

38_A

D

Q

37_A

D

Q

36_A

D

Q

34_A

D

Q

33A

D

Q

32_A

D

Q

31_A

D

Q

30_A

D

Q

29_A

D

Q

28_A

D

Q

27_A

D

Q

26_A

D

Q

25_A

D

Q

24_A

D

Q

23_A

D

Q

21_A

D

Q

20_A

D

Q

9_A

D

Q

8_A

D

Q

7_A

D

Q

6_A

D

Q

5_A

D

Q

4_A

D

Q

2_A

D

Q

1_A

C

B

6_A

C

B

5_A

C

B

4_A

C

B

3_A

C

B

2_A

C

B

1_A

C

B

0_A

D

Q

S

17_A

D

Q

S

7_A

D

Q

S

6_A

D

Q

S

15_A

D

Q

S

5_A

D

Q

S

4_A

D

Q

S

13_A

D

Q

S

3_A

D

Q

S

12_A

D

Q

S

11A

D

Q

S

10_A

D

Q

S

0_A

D

Q

S

9_A

D

Q

S

1_A

D

Q

S

16_A

W

E

_N

_A

C

AS_

N

_

A

R

AS_

N

_

A

M

A

0_A

M

A

4_A

M

A

5_A

M

A

7_A

M

A

6_A

M

A

8_A

M

A

9_A

M

A

11_A

M

A

12_A

B

A

1_A

B

A

0_A

C

S

7_N

_A

C

S

4_N

_A

C

S

3_N

_A

C

S

2_N

_A

C

S

1_N

_A

RCV

E

N

_

O

UT

_

A

RCV

E

N

_

IN_

A

R

ESER

VED

CM

DCL

K

3

_

A

CM

DCL

K

2

_

A

CM

DCL

K

2

_

N

_

A

CM

DCL

K

1

_

N

_

A

CM

DCL

K

0

_

A

CM

DCL

K

0

_

N

_

A

DDRV

RE

F

5

_

A

DDRV

RE

F

4

_

A

DDRV

RE

F

3

_

A

DDRV

RE

F

2

_

A

DDRV

RE

F

1

_

A

D

Q

12_A

D

Q

15_A

D

Q

53_A

D

Q

54_A

D

Q

62_A

D

Q

44_A

M

A

3_A

C

KE_

A

CM

DCL

K

1

_

A

DDRV

RE

F

0

_

A

D

Q

0_A

M

A

10_A

M

A

1_A

M

A

2_A

D

Q

S

8_A

CM

DCL

K

3

_

N

_

A

C

S

6_N

_A

C

S

5_N

_A

C

S

0_N

_A

D

Q

3_A

D

Q

35_A

D

Q

S

2_A

D

Q

S

14_A

DDRCO

M

P

_

A

D

Q

10_A

D

Q

11_A

D

Q

14_A

Address Bus

MCH DDR A

Check Bits

Check Bits

Low Nibble

High Nibble

Low Nibble

High Nibble

Low Nibble

High Nibble

High Nibble

Low Nibble

High Nibble

Low Nibble

High Nibble

Low Nibble

Low Nibble

High Nibble

Low Nibble

High Nibble

Low Nibble

Chip Select

Command Clock

Voltage Ref

Data Group 0

Data Group 0

Data Group 1

Data Group 1

Data Group 2

Data Group 2

Data Group 3

Data Group 3

Data Group 4

Data Group 4

Data Group 5

High Nibble

Data Group 5

Data Group 6

Data Group 6

Data Group 7

Data Group 7

MCH DDR Channel A

R

C

V

_E

N

l

oop s

houl

d be 15 i

n

c

hes

t

o

ta

l rout

e

DDRA

_

RCV

_

E

N

AN

1

6

AK1

7

AK2

4

AK1

9

A

L19

AN

1

7

AF

1

8

A

L17

AG

1

5

AM

4

AE1

1

AH

1

0

AM

2

AM

3

AJ

9

AG

1

0

AM

6

AG

1

2

AN

5

AG

1

1

AH

1

1

AE1

2

AM

1

0

AJ

1

2

AF

1

3

A

L11

AN

1

2

AH

1

3

AE1

4

AG

1

4

AH

1

4

AN

1

3

AK1

4

AJ

1

5

AM

1

3

A

L14

AJ

1

9

AN

2

1

AJ

2

1

AH

2

0

A

L20

AM

2

1

AH

1

9

AF

1

9

AJ

1

8

AM

1

9

AN

2

0

AM

2

4

AN

2

5

A

L25

A

L26

AM

2

8

AN

2

9

AE2

1

AN

2

8

AM

1

5

AG

1

7

AE1

7

AK1

5

A

L16

AH

1

6

AE1

6

AF

1

6

AL

6

AL

8

AM

7

AM

1

2

A

L13

AJ

1

3

AE1

8

AK2

0

AK1

8

AK2

3

AM

2

7

AF

2

1

A

L23

AH

9

AE2

3

AE2

2

AN

2

4

AF

2

4

AG

2

7

AH

2

8

A

L29

A

L28

AK2

9

AM

3

0

AK3

0

AM

3

1

AH

2

3

A

L31

AL

2

AN

8

AH

8

A

L10

AK1

1

AG

2

0

AM

2

2

AM

1

8

AE2

5

AG

2

6

AF

2

5

AH

2

5

AG

2

4

AG

2

3

AJ

2

8

AK2

7

AK2

1

AM

1

6

AL

9

AM

2

5

AJ

2

2

AF

1

2

AM

9

AL

5

AE1

5

AJ

2

7

AE1

9

AJ

2

5

AJ

7

AF

2

2

AJ

2

4

AK2

6

AH

2

6

AJ

1

6

AE2

4

AL

3

AK7

AE1

3

AH

2

2

AF

1

5

AG

1

8

AK1

2

AH

1

7

AG

2

1

AE2

0

A

L22

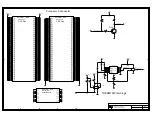

U6

6

DDRA

_

C

K

E

0

16-

20

VREF_DDR_MCH

13,62

0.

1U

F

C

1667

C

1666

0.

01U

F

C

780

0.

1U

F

0.

01U

F

C

779

19

DDRA

_

C

M

DCL

K

3

19

DDRA

_

C

M

DCL

K

3

_

N

18

DDRA

_

C

M

DCL

K

2

18

DDRA

_

C

M

DCL

K

2

_

N

17

DDRA

_

C

M

DCL

K

1

17

DDRA

_

C

M

DCL

K

1

_

N

16

DDRA

_

C

M

DCL

K

0

16

DDRA

_

C

M

DCL

K

0

_

N

R115

6.81

C1145

0.1UF

0.1UF

C1144

C1143

0.1UF

0.

1U

F

C

777

6.

98K

1%

R

524

6.

98K

1%

R

523

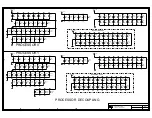

DDRA

_

DRCO

M

P

DDRA

_

M

A

12_R

16-20

DDRA

_

M

A

11_R

16-20

DDRA

_

M

A

10_R

16-20

DDRA

_

M

A

9

_

R

16-20

DDRA

_

M

A

8

_

R

16-20

DDRA

_

M

A

7

_

R

16-20

DDRA

_

M

A

6

_

R

16-20

DDRA

_

M

A

5

_

R

16-20

DDRA

_

M

A

4

_

R

16-20

DDRA

_

M

A

3

_

R

16-20

DDRA

_

M

A

2

_

R

16-20

DDRA

_

M

A

1

_

R

16-20

DDRA

_

M

A

0

_

R

16-20

DDRA

_

R

A

S

_

N_

R

16-20

DDRA

_

C

A

S

_

N_

R

16-20

DDRA

_

W

E

_

N_

R

16-20

DDRA

_

D

Q

3

4

15

DDRA

_

D

Q

3

3

15

DDRA

_

D

Q

3

0

15

DDRA

_

D

Q

2

9

15

DDRA

_

D

Q

S

1

2

15

DDRA

_

D

Q

2

6

15

DDRA

_

D

Q

2

5

15

15

DDRA

_

D

Q

2

3

DDRA

_

D

Q

2

2

15

DDRA

_

D

Q

2

1

15

DDRA

_

D

Q

S

1

1

15

DDRA

_

D

Q

1

8

15

DDRA

_

D

Q

1

7

15

DDRA

_

D

Q

1

4

15

DDRA

_

D

Q

1

3

15

DDRA

_

D

Q

S

1

0

15

DDRA

_

D

Q

9

15

DDRA

_

D

Q

6

15

DDRA

_

D

Q

5

15

DDRA

_

D

Q

S

9

15

DDRA

_

D

Q

2

15

DDRA

_

D

Q

1

15

15

DDRA

_

D

Q

3

DDRA

_

D

Q

0

15

15

DDRA

_

D

Q

7

DDRA

_

D

Q

4

15

15

DDRA

_

D

Q

1

0

DDRA

_

D

Q

8

15

15

DDRA

_

D

Q

1

5

DDRA

_

D

Q

1

2

15

15

DDRA

_

D

Q

1

9

DDRA

_

D

Q

1

6

15

DDRA

_

D

Q

2

0

15

15

DDRA

_

D

Q

2

7

DDRA

_

D

Q

2

4

15

15

DDRA

_

D

Q

3

1

DDRA

_

D

Q

2

8

15

15

DDRA

_

D

Q

3

5

DDRA

_

D

Q

3

2

15

DDRA

_

D

Q

S

1

3

15

DDRA

_

D

Q

3

7

15

DDRA

_

D

Q

3

8

15

15

DDRA

_

D

Q

3

9

DDRA

_

D

Q

3

6

15

DDRA

_

D

Q

4

1

15

DDRA

_

D

Q

4

2

15

15

DDRA

_

D

Q

4

3

DDRA

_

D

Q

4

0

15

DDRA

_

D

Q

S

1

4

15

15

DDRA

_

D

Q

4

4

15

DDRA

_

D

Q

4

6

DDRA

_

D

Q

4

5

15

DDRA

_

D

Q

4

9

15

DDRA

_

D

Q

5

0

15

15

DDRA

_

D

Q

5

1

DDRA

_

D

Q

4

8

15

DDRA

_

D

Q

S

1

5

15

DDRA

_

D

Q

5

3

15

15

DDRA

_

D

Q

5

4

DDRA

_

D

Q

5

2

15

DDRA

_

D

Q

5

6

15

DDRA

_

D

Q

5

7

15

DDRA

_

D

Q

5

9

15

15

DDRA

_

D

Q

5

8

DDRA

_

D

Q

6

0

15

DDRA

_

D

Q

S

1

6

15

DDRA

_

D

Q

6

1

15

15

DDRA

_

D

Q

6

2

DDRA

_

C

B

1

15

15

DDRA

_

C

B

2

DDRA

_

C

B

3

15

DDRA

_

C

B

0

15

DDRA

_

C

B

4

15

15

DDRA

_

C

B

5

15

DDRA

_

C

B

7

DDRA

_

C

B

6

15

R

841

47

DDRCV

O

H

_

A

DDRA

_

C

S

0

_

N

_

R

16,

20

DDRA

_

C

S

1

_

N

_

R

16,

20

DDRA

_

C

S

2

_

N

_

R

17,

20

DDRA

_

C

S

3

_

N

_

R

17,

20

DDRA

_

C

S

4

_

N

_

R

18,

26

DDRA

_

C

S

5

_

N

_

R

18,

26

DDRA

_

C

S

6

_

N

_

R

19,

20

DDRA

_

C

S

7

_

N

_

R

19,

20

DDRA

_

D

Q

S

7

15

DDRA

_

D

Q

S

1

7

15

DDRA

_

B

A

0

_

R

16-20

DDRA

_

B

A

1

_

R

16-19,

26

DDRA

_

D

Q

S

0

15

DDRA

_

D

Q

S

1

15

DDRA

_

D

Q

S

2

15

DDRA

_

D

Q

S

3

15

DDRA

_

D

Q

S

4

15

DDRA

_

D

Q

S

5

15

DDRA

_

D

Q

S

6

15

DDRA

_

D

Q

S

8

15

R

522

13K

C

778

0.

01U

F

13K

R

521

DDRCV

O

L

_

A

DDRA

_

D

Q

6

3

15

DDRA

_

D

Q

5

5

15

DDRA

_

D

Q

4

7

15

DDRA

_

D

Q

1

1

15

0.

01U

F

C

1668

C

1669

0.

1U

F

12

Содержание Xeon

Страница 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Страница 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Страница 34: ...Platform Stack Up and Component Placement Overview 34 Design Guide This page is intentionally left blank ...

Страница 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Страница 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Страница 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Страница 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Страница 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Страница 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Страница 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Страница 222: ...Schematics 222 Design Guide This page is intentionally left blank ...