Design Guide

69

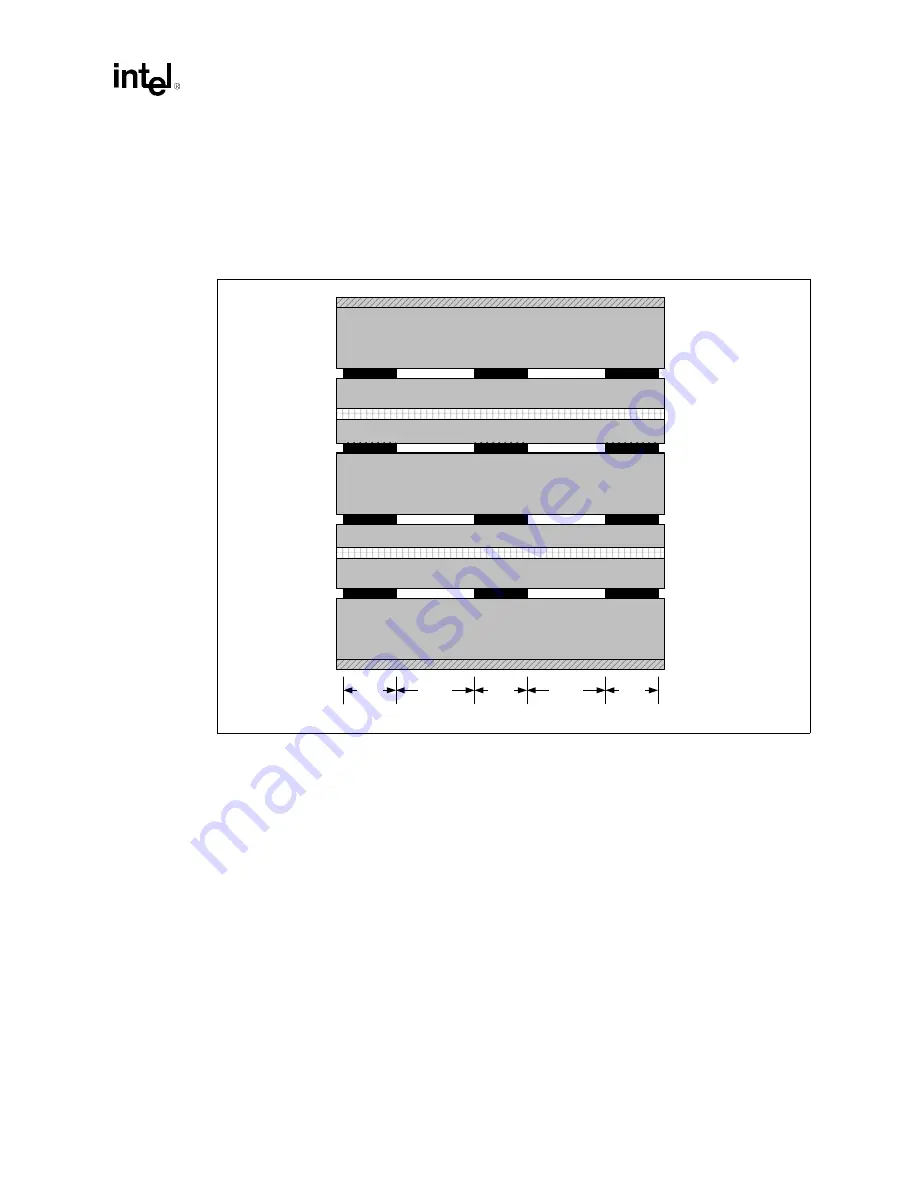

Memory Interface Routing Guidelines

The DDR interface requires a nominal impedance (Zo) of 50

Ω

± 10%. Using the recommended

stackup, all routing layers yield 50

Ω

nominal impedance when using 5 mil wide traces. Route all

DDR signals 5/15 (5 mils wide with 15 mil spacing) as shown in

with the exception of

CKE, CMDCLK[3:0], and CMDCLK[3:0]#. For CMDCLK routing rules, refer to

and

. For CKE routing rules, refer to

. Route layers 4 and 5

orthogonal to each other to minimize crosstalk.

NOTES:

1. Traces on layers 4 and 5 must be routed orthogonally to each other to minimize the effects of crosstalk.

2. Source Synch., Source Clocked, and CS# are routed 5/15.

3. CKE is routed 7.5/15.

Figure 6-3. Trace Width and Spacing for All DDR Signals Except CMDCLK/CMDCLK#

Core 5.2 mil

Dielectric 9.6 mil

2.1 mil (1 oz + plating)

Power

Dielectric

Power

Dielectric

Ground

Main Core

Dielectric

Core

Ground

Dielectric

Core

1.4 mil (1 oz)

2.1 mil (1 oz + plating)

Core 5.2 mil

Dielectric 4.3 mil

Core 14.0 mil

Dielectric 9.6 mil

Dielectric 4.3 mil

Layer 1

Layer 2

Layer 3

Layer 4

Layer 5

Layer 6

Layer 7

Layer 8

Signal

Signal

Signal

Signal

Signal

Signal

Signal

Signal

Signal

Trace

Width

1.4 mil (1 oz)

1.4 mil (1 oz)

Signal

Signal

1.4 mil (1 oz)

1.4 mil (1 oz)

1.4 mil (1 oz)

Signal

Trace

Spacing

Trace

Spacing

Trace

Width

Trace

Width

Содержание Xeon

Страница 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Страница 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Страница 34: ...Platform Stack Up and Component Placement Overview 34 Design Guide This page is intentionally left blank ...

Страница 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Страница 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Страница 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Страница 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Страница 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Страница 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Страница 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Страница 222: ...Schematics 222 Design Guide This page is intentionally left blank ...