SCHOTTKY

-

+

270U

F

+

+

+

+V5_0

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

1.0UH

1.0UH

+

F

D

S

6690S

S

D

G

VTT_DDR

+

F

D

S

6690S

S

D

G

+V5_0

+V2_5

1.5UH

270U

F

+

+V3_3

FAN5066

V

CCA

V

CCP

VFB

IFB

LODRV

HIDRV

VCCQP

G

NDA

G

NDD

G

NDP

_

1

G

NDP

CEXT

VREF

PWRGOOD

ENABLE

VID4

VID3

VID2

VID1

VID0

+

+

+V2_5

+V5_0

LM2904

8

7

6

5

4

3

2

1

M

B

R

0520

M

B

R

S

130T

3

M

B

R

S

130T

3

+

SCHOT

T

K

Y

-

+

SCHOT

T

K

Y

-

+

+V5_0

F

D

S

6688

G

D

S

F

D

S

6688

G

D

S

F

D

S

6688

G

D

S

F

D

S

6688

G

D

S

F

D

S

6688

G

D

S

F

D

S

6688

G

D

S

F

D

S

6688

G

D

S

F

D

S

6688

G

D

S

PLLFLTR

PLLIN

NC1

SW1

VOS+

VOS-

EAIN

VDIFFO

SGND

ITH

NC2

BOOST1

BG1

SENSE1-

RUN/SS

VIN

EXTVCC

PGOOD

TG2

BOOST2

SW2

PGND

BG2

INTVCC

SENSE2-

TG1

LT

C

_1929-

PG

-S

L25101

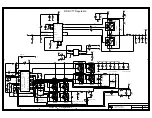

Route as diff pair

Place between

Drive Power Ground

Place between

VR pins 13, 14

VR pins 2,3

C1112 across Q1,Q2

C1114 across Q3,Q4

C1113 across Q5,Q6

C1115 across Q7,Q8

Route as diff pair

originating near DIMMs

Route as diff pair

Place caps close to high-side FETs

DDR VTT Regulation

DDR V2_5 Regulation

Small Signal Ground

Place C1124 between

VR pins 20, 21

62

100

R

430

5

6

7

26

12

11

4

10

9

8

28

25

23

2

3

1

24

22

15

16

18

17

20

19

21

14

13

27

U1

1

2

5

8

7

6

3

4

Q8

4

3

6

7

8

5

2

1

Q7

1

2

5

8

7

6

3

4

Q4

4

3

6

7

8

5

2

1

Q3

1

2

5

8

7

6

3

4

Q2

1

2

5

8

7

6

3

4

Q6

4

3

6

7

8

5

2

1

Q5

V2_5SENSE1_P

4

3

6

7

8

5

2

1

Q1

1929_VOS_M

1929_VOS_P

U103_VREF_DDR

U103_VDIV

U104_VREF

U104_VID0

V2_5_L1

V2_5_L2

VTT_DDR_L

1U

F

C

1506

C

1115

1U

F

1U

F

C

1114

C

1113

1U

F

1U

F

C

1112

0

R957

R956

0

0

R436

R435

0

R

434

0

0

R

433

R431

10K

10K

R

422

R748

1%

10K

10K 1%

R749

0.

1U

F

C

1597

0.

1U

F

C

1508

0.

1U

F

C

1507

C

1504

0.

1U

F

0.

1U

F

C

1503

C

1501

0.

1U

F

C1124

1UF

C

1502

1U

F

100P

F

C

1505

10U

F

C

705

C

704

10U

F

10U

F

C

703

C

702

10U

F

1000P

F

C

1575

C

635

1000P

F

C

632

100P

F

C631

0.01UF

3

1

CR5

3

1

CR6

2

1

10UF

C706

2

1

CR4

C

634

100P

F

C1576

1000PF

1

2

CR7

R

427

NO

P

O

P

4

C

633

100P

F

8.

06K

R

424

1%

R

423

17.

4K

1%

C

1128

0.

47U

F

C1126

0.1UF

0.1UF

C1125

1

2

CR7

4

VREF_DDR_DIMM

16-19,22-25

VREF_DDR_MCH

12,13

RC5051_ENABLE

8

7

6

5

4

3

2

1

U103

2

1

1000U

F

C

657

12

C

656

1000U

F

6

7

5

4

9

12

13

15

14

11

10

1

16

3

2

8

17

18

19

20

U104

63

1_2_LT1735_PGOOD

1M

R

429

2

1

C

1577

V2_5SENSE2_M

V2_5SENSE2_P

2

1

L18

4.7

R751

R750

4.7

0.002

R426

R425

0.002

R421

10

1

2

3

4

5

6

7

8

Q43

1929_PGOOD

64

R

752

10K

2

1

820U

F

C

1484

8

7

6

5

4

3

2

1

Q44

R

428

NO

P

O

P

4

12

C

1481

820U

F

1

2

L8

2

1

L7

0.

47U

F

C

1127

2

1

820U

F

C

1482

12

C

1483

820U

F

V2_5SENSE1_M

12

C

1479

1

3

CR80

VQP

LODRV

HIDRV

VTT_DDR_PGOOD

64

Содержание Xeon

Страница 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Страница 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Страница 34: ...Platform Stack Up and Component Placement Overview 34 Design Guide This page is intentionally left blank ...

Страница 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Страница 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Страница 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Страница 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Страница 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Страница 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Страница 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Страница 222: ...Schematics 222 Design Guide This page is intentionally left blank ...