+V2_5

+V1_2

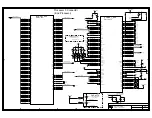

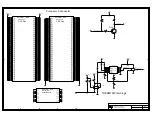

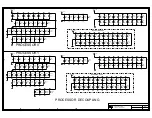

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

+V1_2

+V1_2

+V1_2

+V1_2

+V1_2

+V3_3

SM

B_

D

A

T

A

SM

B_

C

L

K

H

I0_A

H

I0_B

H

I0_C

H

I0_D

H

I10_A

H

I10_B

H

I10_C

H

I10_D

H

I11_A

H

I11_B

H

I11_C

H

I11_D

H

I12_B

H

I12_C

H

I12_D

H

I13_B

H

I13_C

H

I13_D

H

I14_B

H

I14_D

H

I15_B

H

I15_C

H

I15_D

H

I16_B

H

I16_C

H

I16_D

H

I17_B

H

I17_C

H

I17_D

H

I18_B

H

I18_D

H

I1_A

H

I1_B

H

I1_C

H

I1_D

H

I20_B

H

I20_D

H

I21_B

H

I21_D

H

I2_A

H

I2_B

H

I2_C

H

I2_D

H

I3_A

H

I3_B

H

I3_C

H

I3_D

H

I4_A

H

I4_B

H

I4_C

H

I4_D

H

I5_A

H

I5_B

H

I5_C

H

I5_D

H

I6_A

H

I6_B

H

I6_C

H

I6_D

H

I7_A

H

I7_B

H

I7_C

H

I7_D

H

I8_A

H

I8_B

H

I8_C

H

I8_D

H

I9_A

H

I9_B

H

I9_C

H

I9_D

HIS

W

NG

_

B

HIS

W

NG

_

C

HIS

W

NG

_

D

H

IVR

EF

_

B

H

IVR

EF

_

C

H

IVR

EF

_

D

HI_

RCO

M

P

_

A

HI_

RCO

M

P

_

B

HI_

RCO

M

P

_

C

HI_

RCO

M

P

_

D

PST

R

B

F

_

A

PST

R

BS_

A

PST

R

BS_

B

PU

ST

R

B

F

_

B

PU

ST

R

BS_

B

PST

R

B

F

_

C

PST

R

BS_

C

PU

ST

R

B

F

_

C

PU

ST

R

BS_

C

PST

R

B

F

_

D

PST

R

BS_

D

PU

ST

R

B

F

_

D

PU

ST

R

BS_

D

H

I18_C

H

I20_C

H

I21_C

PST

R

B

F

_

B

H

I14_C

RS

T

IN_

N

HI_

V

RE

F

_

A

HIS

W

NG

_

A

CL

K

6

6

R

ESER

VED

0

1

R

ESER

VED

0

2

Hub Interface C

Hub Interface B

Hub Interface D

Hub Interface A

MCH Hub Interfaces

MCH

S

L

OT

_D

_H

I2

0

52

S

L

OT

_D

_H

I1

7

52

S

L

OT

_D

_H

I1

6

52

S

L

OT

_D

_H

I0

S

L

OT

_D

_H

I3

S

L

OT

_D

_H

I9

S

L

OT

_D

_H

I1

4

S

L

OT

_D

_H

I1

3

S

L

OT

_D

_H

I1

2

S

L

OT

_D

_H

I1

1

S

L

OT

_D

_H

I1

0

S

L

OT

_D

_H

I8

S

L

OT

_D

_H

I7

S

L

OT

_D

_H

I4

S

L

OT

_D

_H

I2

S

L

OT

_D

_H

I1

S

L

OT

_D

_H

I6

S

L

OT

_D

_H

I5

S

L

OT

_D

_H

I[15:

0]

52

S

L

OT

_D

_H

I1

5

SL

O

T

_

D

_

PST

R

B

F

52

SL

O

T

_

D

_

PST

R

B

S

52

S

L

OT

_D

_P

U

S

T

R

B

F

52

S

L

OT

_D

_P

U

S

T

R

B

S

52

11

B3

1

J2

5

E1

1

D1

6

D2

2

D2

8

F1

1

A1

3

B2

0

A2

5

G12

C1

3

C1

9

D2

4

D1

2

B1

8

A2

4

E1

2

C1

8

E2

3

C1

1

F2

3

J1

4

F1

7

F2

2

H1

4

B2

1

H2

3

B1

7

C2

4

H2

5

E1

4

F2

5

B1

1

G16

B2

4

G25

F1

4

E2

7

G13

H2

1

G10

C1

7

G18

G26

F1

0

C1

6

C2

2

F2

6

D9

A1

7

E2

0

G24

E9

A1

6

F1

9

A2

7

J1

1

B1

4

D2

1

H2

4

H9

D1

5

E2

1

C2

6

J1

3

C1

4

D1

9

G22

J1

0

F1

3

A2

0

E2

4

B1

5

H1

7

F2

4

D1

3

A2

1

J2

2

H1

1

E1

5

C2

0

G21

C1

0

D1

0

H1

5

A1

2

B1

2

C2

3

B2

3

D1

8

E1

7

D2

7

D2

6

B2

5

C2

5

F2

0

H1

8

F1

6

G15

E1

8

E2

8

G9

H1

2

J1

6

D2

9

B3

0

U6

6

S

L

OT

_D

_H

I1

8

52

S

L

OT

_D

_H

I2

1

52

P

64H

2_1_P

U

S

T

R

B

S

29

P

64H

2_1_P

U

S

T

R

B

F

29

P

64H

2_1_P

S

T

R

B

S

29

P

64H

2_1_P

S

T

R

B

F

29

P

64H

2_1_H

I1

5

P

64H

2_1_H

I[1

5:

0]

29

P

64H

2_1_H

I5

P

64H

2_1_H

I0

P

64H

2_1_H

I1

4

P

64H

2_1_H

I1

3

P

64H

2_1_H

I1

2

P

64H

2_1_H

I1

1

P

64H

2_1_H

I1

0

P

64H

2_1_H

I9

P

64H

2_1_H

I8

P

64H

2_1_H

I7

P

64H

2_1_H

I6

P

64H

2_1_H

I4

P

64H

2_1_H

I3

P

64H

2_1_H

I2

P

64H

2_1_H

I1

P

64H

2_1_H

I1

6

29

P

64H

2_1_H

I1

7

29

P

64H

2_1_H

I1

8

29

P

64H

2_1_H

I2

0

29

P

64H

2_1_H

I2

1

29

P

64H

2_2_P

U

S

T

R

B

S

33

P

64H

2_2_P

U

S

T

R

B

F

33

P

64H

2_2_P

S

T

R

B

S

33

P

64H

2_2_P

S

T

R

B

F

33

P

64H

2_2_H

I1

5

P

64H

2_2_H

I1

4

P

64H

2_2_H

I1

3

P

64H

2_2_H

I1

2

P

64H

2_2_H

I1

1

P

64H

2_2_H

I1

0

P

64H

2_2_H

I6

P

64H

2_2_H

I5

P

64H

2_2_H

I4

P

64H

2_2_H

I3

P

64H

2_2_H

I1

P

64H

2_2_H

I9

P

64H

2_2_H

I0

P

64H

2_2_H

I7

P

64H

2_2_H

I8

33

P

64H

2_2_H

I[15:

0]

P

64H

2_2_H

I2

P

64H

2_2_H

I1

6

33

33

P

64H

2_2_H

I1

7

P

64H

2_2_H

I1

8

33

P

64H

2_2_H

I2

0

33

P

64H

2_2_H

I2

1

33

M

CH_

RS

V

D

_

0

1

M

CH_

RS

V

D

_

0

2

R775

4.7K

24.

9

R

111

1%

R

107

24.

9

1%

HI_

RCO

M

P

_

C

24.9

R105

1%

R100

24.9

1%

392

R

114

1%

R

109

392

1%

392

R

104

1%

R

102

392

1%

HI_

RCO

M

P

_

A

HI_VSWING_B

11

HI_VSWING_A

11

H

I_

VSW

IN

G

_

B

11

H

I_

VSW

IN

G

_

A

11

I2

C

_

B

U

S

2_C

LK

4,

6,

80,

81

I2

C

_

BU

S2

_

D

AT

4,

6,

80,

81

ICH3

_

P

S

T

RB

S

53

ICH3

_

P

S

T

RB

F

53

M

CH_

CL

K

6

6

65

HI_VREF_B

11

HI_

V

RE

F

_

B

11

HI_

RCO

M

P

_

B

PCIRST2_5_N

16-19,22-25,53

R

740

100

HI_

V

RE

F

_

A

11

HI_VREF_A

11

R

108

499

499

R

113

R

110

453

453

R

112

HI_

V

RE

F

_

D

453

R106

499

R

103

R

101

499

R99

453

C

598

0.

01U

F

0

.01U

F

C

595

C

596

0.

01U

F

0.

01U

F

C

909

0.

1U

F

C

913

C

908

0.

1U

F

0.

1U

F

C

905

0.

01U

F

C

597

IC

H

3_H

I[11:

0]

53

IC

H

3_H

I1

1

IC

H

3_H

I1

IC

H

3_H

I2

IC

H

3_H

I3

IC

H

3_H

I4

IC

H

3_H

I5

IC

H

3_H

I6

IC

H

3_H

I7

IC

H

3_H

I8

IC

H

3_H

I9

IC

H

3_H

I1

0

IC

H

3_H

I0

HI_

RCO

M

P

_

D

HI_

V

RE

F

_

C

H

I_

VSW

IN

G

_

D

H

I_

VSW

IN

G

_

C

C

906

0.

1U

F

0.

1U

F

C

907

C

910

0.

01U

F

0

.01U

F

C

911

C

912

0.

01U

F

C

914

0.

1U

F

0.

1U

F

C

915

C

916

0.

1U

F

R948

1K

Содержание Xeon

Страница 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Страница 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Страница 34: ...Platform Stack Up and Component Placement Overview 34 Design Guide This page is intentionally left blank ...

Страница 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Страница 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Страница 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Страница 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Страница 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Страница 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Страница 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Страница 222: ...Schematics 222 Design Guide This page is intentionally left blank ...