OVERVIEW OF THE 80C186 FAMILY ARCHITECTURE

2-48

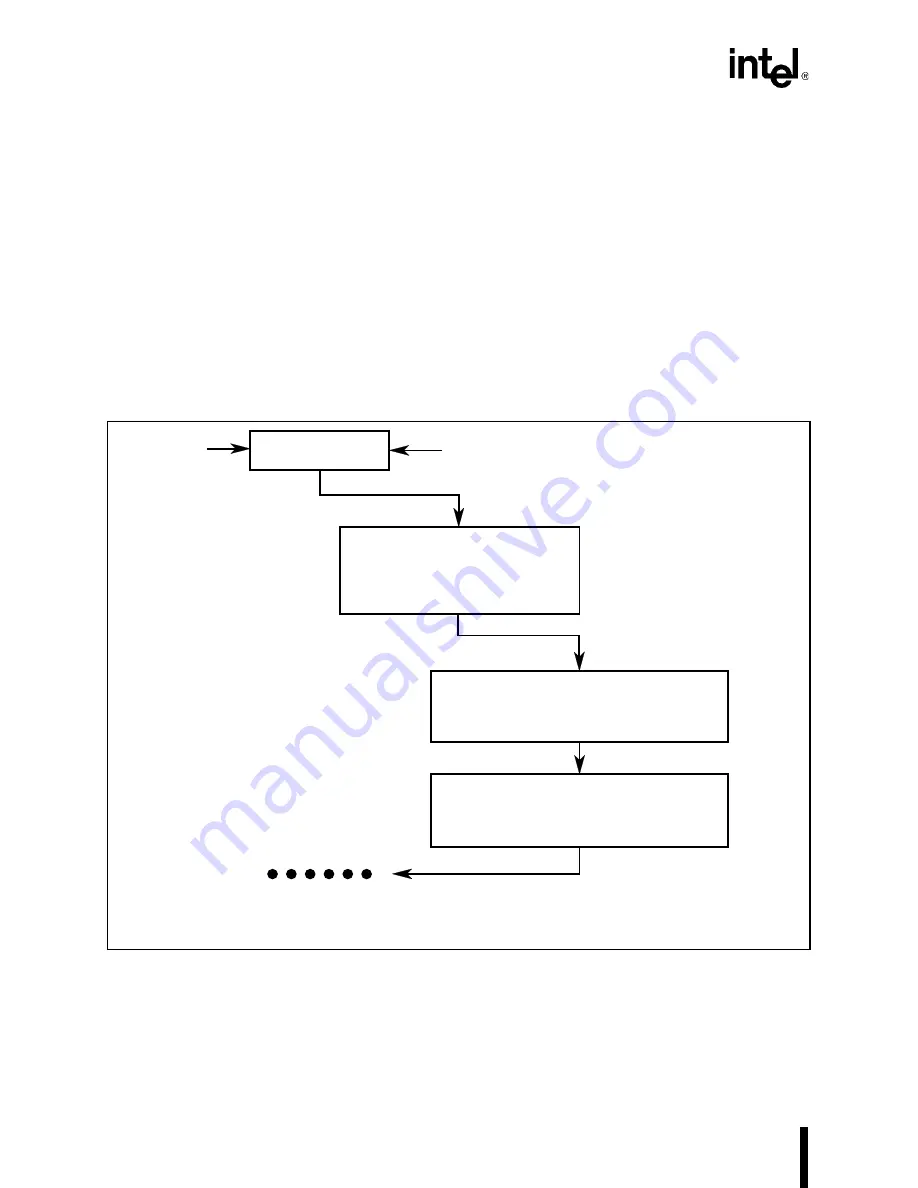

Single step priority is a special case. If an interrupt (NMI or maskable) occurs at the same instruc-

tion boundary as a single step, the interrupt vector is taken first, then is followed immediately by

the single step vector. However, the single step service routine is executed before the interrupt

service routine (see Figure 2-29). If the single step service routine re-enables single step by exe-

cuting the IRET, the interrupt service routine will also be single stepped. This can severely limit

the real-time response of the CPU to an interrupt.

To prevent the single-step routine from executing before a maskable interrupt, disable interrupts

while single stepping an instruction, then enable interrupts in the single step service routine. The

maskable interrupt is serviced from within the single step service routine and that interrupt ser-

vice routine is not single-stepped. To prevent single stepping before an NMI, the single-step ser-

vice routine must compare the return address on the stack to the NMI vector. If they are the same,

return to the NMI service routine immediately without executing the single step service routine.

Figure 2-29. Simultaneous NMI and Single Step Interrupts

The most complicated case is when an NMI, a maskable interrupt, a single step and another ex-

ception are pending on the same instruction boundary. Figure 2-30 shows how this case is prior-

itized by the CPU. Note that if the single-step routine sets the Trap Flag (TF) bit before executing

the IRET instruction, the NMI routine will also be single stepped.

NMI

IRET

Instruction

Trap Flag = 1

Push PSW, CS, IP

Fetch Divide Error Vector

Trap Flag = 0

Execute Single Step

Service Routine

Push PSW, CS, IP

Fetch Single Step Vector

Trap Flag = ???

A1032-0A

Содержание 80C186EA

Страница 1: ...80C186EA 80C188EA Microprocessor User s Manual...

Страница 2: ...80C186EA 80C188EA Microprocessor User s Manual 1995...

Страница 19: ......

Страница 20: ...1 Introduction...

Страница 21: ......

Страница 28: ...2 Overview of the 80C186 Family Architecture...

Страница 29: ......

Страница 79: ......

Страница 80: ...3 Bus Interface Unit...

Страница 81: ......

Страница 129: ......

Страница 130: ...4 Peripheral Control Block...

Страница 131: ......

Страница 139: ......

Страница 140: ...5 ClockGenerationand Power Management...

Страница 141: ......

Страница 165: ......

Страница 166: ...6 Chip Select Unit...

Страница 167: ......

Страница 190: ...7 Refresh Control Unit...

Страница 191: ......

Страница 205: ......

Страница 206: ...8 Interrupt Control Unit...

Страница 207: ......

Страница 239: ...INTERRUPT CONTROL UNIT 8 32...

Страница 240: ...9 Timer Counter Unit...

Страница 241: ......

Страница 265: ......

Страница 266: ...10 Direct Memory Access Unit...

Страница 267: ......

Страница 295: ...DIRECT MEMORY ACCESS UNIT 10 28...

Страница 296: ...11 Math Coprocessing...

Страница 297: ......

Страница 314: ...12 ONCE Mode...

Страница 315: ......

Страница 318: ...A 80C186 Instruction Set Additions and Extensions...

Страница 319: ......

Страница 330: ...B Input Synchronization...

Страница 331: ......

Страница 334: ...C Instruction Set Descriptions...

Страница 335: ......

Страница 383: ...INSTRUCTION SET DESCRIPTIONS C 48...

Страница 384: ...D Instruction Set Opcodes and Clock Cycles...

Страница 385: ......

Страница 408: ...Index...

Страница 409: ......