20 i

2

C MaSTeR (i2CM)

20-8

Seiko epson Corporation

S1C17624/604/622/602/621 TeChniCal Manual

i

2

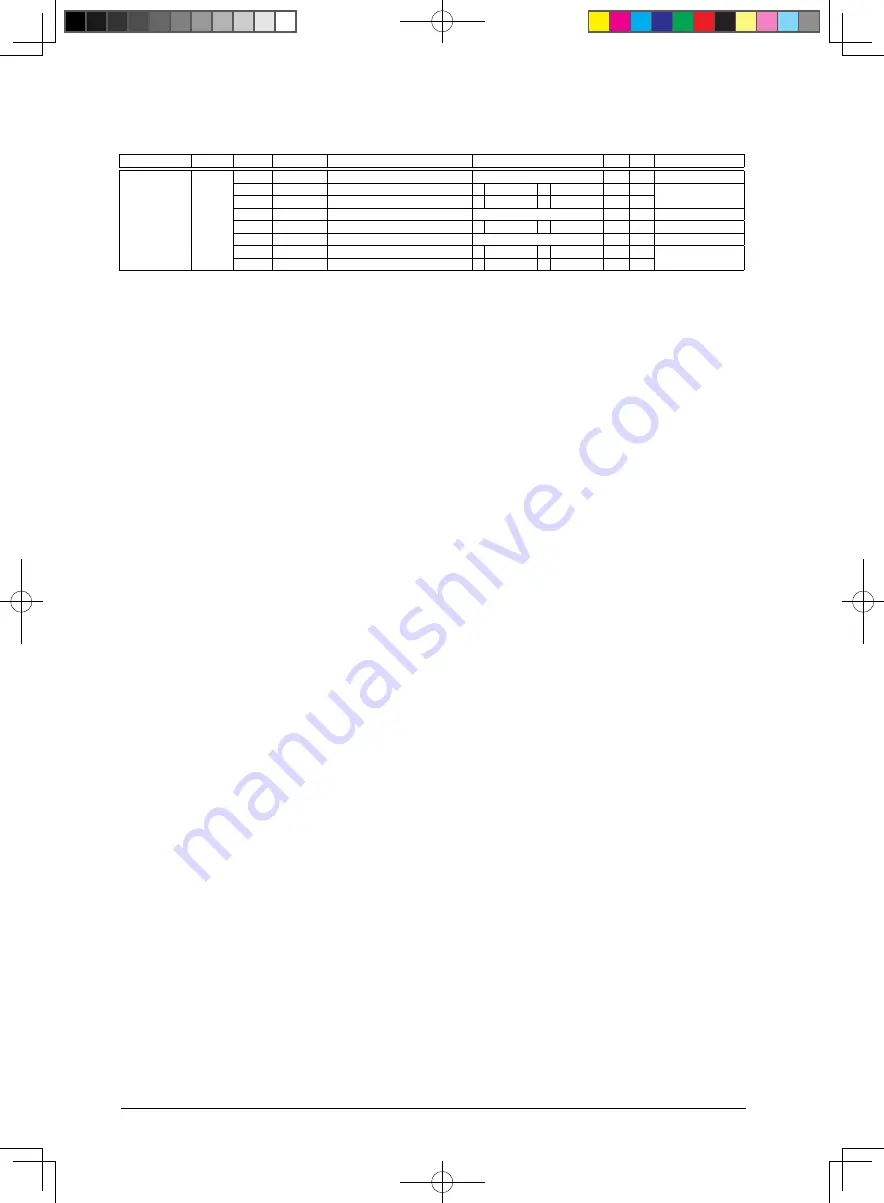

C Master Control Register (i2CM_CTl)

Register name address

Bit

name

Function

Setting

init. R/W

Remarks

i

2

C Master Con-

trol Register

(i2CM_CTl)

0x4342

(16 bits)

D15–10 –

reserved

–

–

–

0 when being read.

D9

RBuSY

Receive busy flag

1 Busy

0 Idle

0

R

D8

TBuSY

Transmit busy flag

1 Busy

0 Idle

0

R

D7–5 –

reserved

–

–

–

0 when being read.

D4

nSeRM

Noise remove on/off

1 On

0 Off

0

R/W

D3–2 –

reserved

–

–

–

0 when being read.

D1

STP

Stop control

1 Stop

0 Ignored

0

R/W

D0

STRT

Start control

1 Start

0 Ignored

0

R/W

D[15:10] Reserved

D9

RBuSY: Receive Busy Flag Bit

Indicates the I2CM receiving status.

1 (R):

Operating

0 (R):

Standby (default)

RBUSY is set to 1 when the I2CM starts data receiving and is maintained at 1 while receiving is under-

way. It is cleared to 0 once reception is completed.

D8

TBuSY: Transmit Busy Flag Bit

Indicates the I2CM transmission status.

1 (R):

Operating

0 (R):

Standby (default)

TBUSY is set to 1 when the I2CM starts data transmission and is maintained at 1 while transmission is

underway. It is cleared to 0 once transmission is completed.

D[7:5]

Reserved

D4

nSeRM: noise Remove On/Off Bit

Turns the noise filter function on or off.

1 (R/W): On

0 (R/W): Off (default)

The I2CM module includes a function for filtering noise from the SDA0 and SCL0 pin input signals.

This function is enabled by setting NSERM to 1. Note that using this function requires setting the I2CM

clock (T16 Ch.2 output clock) frequency to 1/6 or less of PCLK.

D[3:2]

Reserved

D1

STP: Stop Control Bit

Generates the stop condition.

1 (R/W): Stop condition generated

0 (R/W): Ineffective (default)

By setting STP to 1, the I2CM module generates the stop condition by pulling up the I

2

C bus SDA line

from Low to High with the SCL line maintaining at High. The I

2

C bus subsequently becomes free. Note

that the stop condition will be generated only if STP is 1 and TXE/I2CM_DAT register, RXE/I2CM_

DAT register, and STRT are set to 0 when data transfer is completed (including ACK transfer). STP is

automatically reset to 0 if the stop condition is generated.

D0

STRT: Start Control Bit

Generates the start condition.

1 (R/W): Start condition generated

0 (R/W): Ineffective (default)

By setting STRT to 1, the I2CM module generates the start condition by pulling down the I

2

C bus SDA

line to Low with SCL line maintaining at High.

The repeated start condition can be generated by setting STRT to 1 when the I

2

C bus is busy.

STRT is automatically reset to 0 once the start condition or repeated start condition is generated. The

I

2

C bus subsequently becomes busy.