20 i

2

C MaSTeR (i2CM)

S1C17624/604/622/602/621 TeChniCal Manual

Seiko epson Corporation

20-5

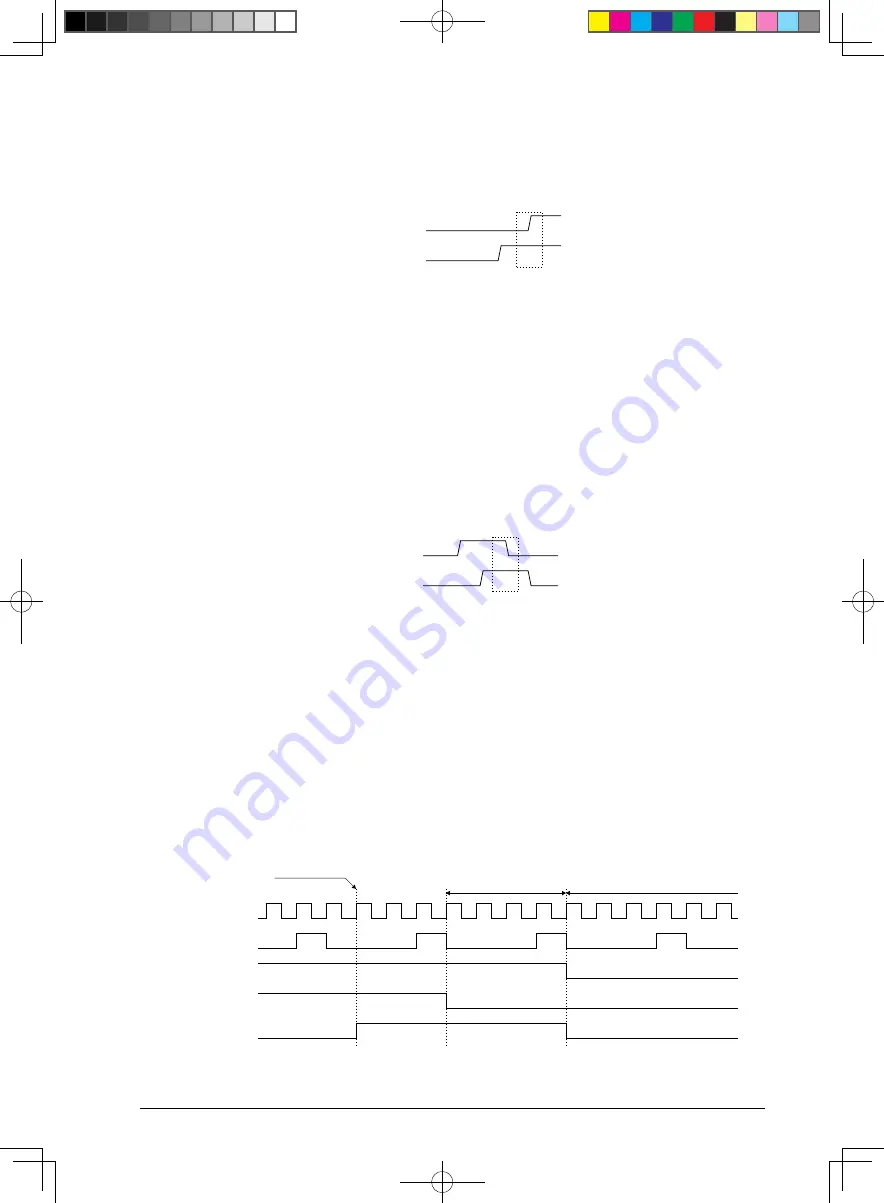

end of data transfers (Generating stop condition)

To end data transfers after all data has been transferred, the I

2

C master (this module) must generate a stop con-

dition. The stop condition applies when the SCL line is maintained at High and the SDA line is pulled up from

Low to High.

SDA0 (output)

SCL0 (output)

Stop condition

5.4 Stop Condition

Figure 20.

The stop condition is generated by setting STP/I2CM_CTL register to 1.

When STP is set to 1, the I2CM module pulls up the I

2

C bus SDA line from Low to High with the SCL line

maintained at High to generates a stop condition. The I

2

C bus subsequently switches to free state.

Before STP can be set to 1, confirm that TBUSY or RBUSY is reset to 0 from 1 (this indicates that the I2CM

module has finished data transmit/receive operation) and then make the wait time longer than 1/4 of the I

2

C

clock cycle set. When generating a stop condition to the slave device with a clock stretch function, STP must be

set to 1 after data transfer (including ACK/NAK transfer) has finished and the time for the slave device to finish

clock stretching has elapsed. STP is reset to 0 when the stop condition is generated.

Continuing data transfer (Generating Repeated start condition)

To make it possible to continue with a different data transfer after data transfer completion, the I

2

C master (this

module) can generate a repeated start condition.

SDA0 (output)

SCL0 (output)

Repeated start condition

5.5 Repeated Start Condition

Figure 20.

The repeated start condition is generated by setting STRT/I2CM_CTL register to 1 when the I

2

C bus is busy.

STRT is automatically reset to 0 once the repeated start condition is generated. Slave address transmission is

subsequently possible with the I

2

C bus remaining in the busy state.

Disabling data transfer

After the stop condition has been generated, write 0 to I2CMEN to disable data transfers. To determine whether

the stop condition has been generated, check to see if STP is automatically cleared to 0 after it is set to 1 by

polling.

When I2CMEN is set to 0 while the I

2

C bus is in busy status, the SCL0 and SDA0 output levels and transfer

data at that point cannot be guaranteed.

Timing chart

PCLK

T16 Ch.2 output

SCL0

SDA0

STRT

STRT setting

Start condition

I

2

C bus busy

5.6 Start Condition Generation

Figure 20.