21 i

2

C SlaVe (i2CS)

S1C17624/604/622/602/621 TeChniCal Manual

Seiko epson Corporation

21-5

When the asynchronous address detection function is used, the data written before ASDET_EN is reset to 0

becomes invalid. Therefore, transmission data must be written after TXEMP has been set to 1.

When the clock stretch function is enabled

The master device is placed into wait status by the clock stretch function, so transmit data can be written

after TXEMP is set. However, if the previous transmit data is still stored in SDATA[7:0], it will be sent im-

mediately after TXEMP has been set. In order to avoid this problem, clear the I2CS_TRNS register using

TBUF_CLR/I2CS_CTL register before this module is selected as the slave device. The I2CS_TRNS regis-

ter is cleared by writing 1 to TBUF_CLR then writing 0 to it.

It is not necessary to clear the I2CS_TRNS register if the first transmit data is written before TXEMP has

been set.

When the asynchronous address detection function is used, the data written before ASDET_EN is reset to 0

becomes invalid. Therefore, transmission data must be written after TXEMP has been set to 1.

For writing transmit data other than the first time, use an interrupt that can be generated when TXEMP is set

to 1. TXEMP is also set to 1 when the transmit data written to SDATA[7:0] is loaded to the sift register during

transmission. TXEMP is cleared by writing transmit data to SDATA[7:0].

When the clock stretch function is disabled (default)

When the clock stretch function has been disabled, data must be written to the I2CS_TRNS register within

7 cycles of the I

2

C clock (SCL1 input clock) from TXEMP being set to 1.

If data has not been written in this period, the current register value (previous transmit data) will be sent.

In this case, TXUDF/I2CS_STAT register is set to 1 to indicate that invalid data has been sent. An interrupt

can be generated when TXUDF is set to 1, so an error handling should be performed in the interrupt han-

dler routine. TXUDF is cleared by writing 1.

When the clock stretch function is enabled

When the clock stretch function has been enabled, the I2CS module pulls down the SCL1 pin to low to gen-

erate a clock stretch (wait) status until transmit data is written to the I2CS_TRNS register.

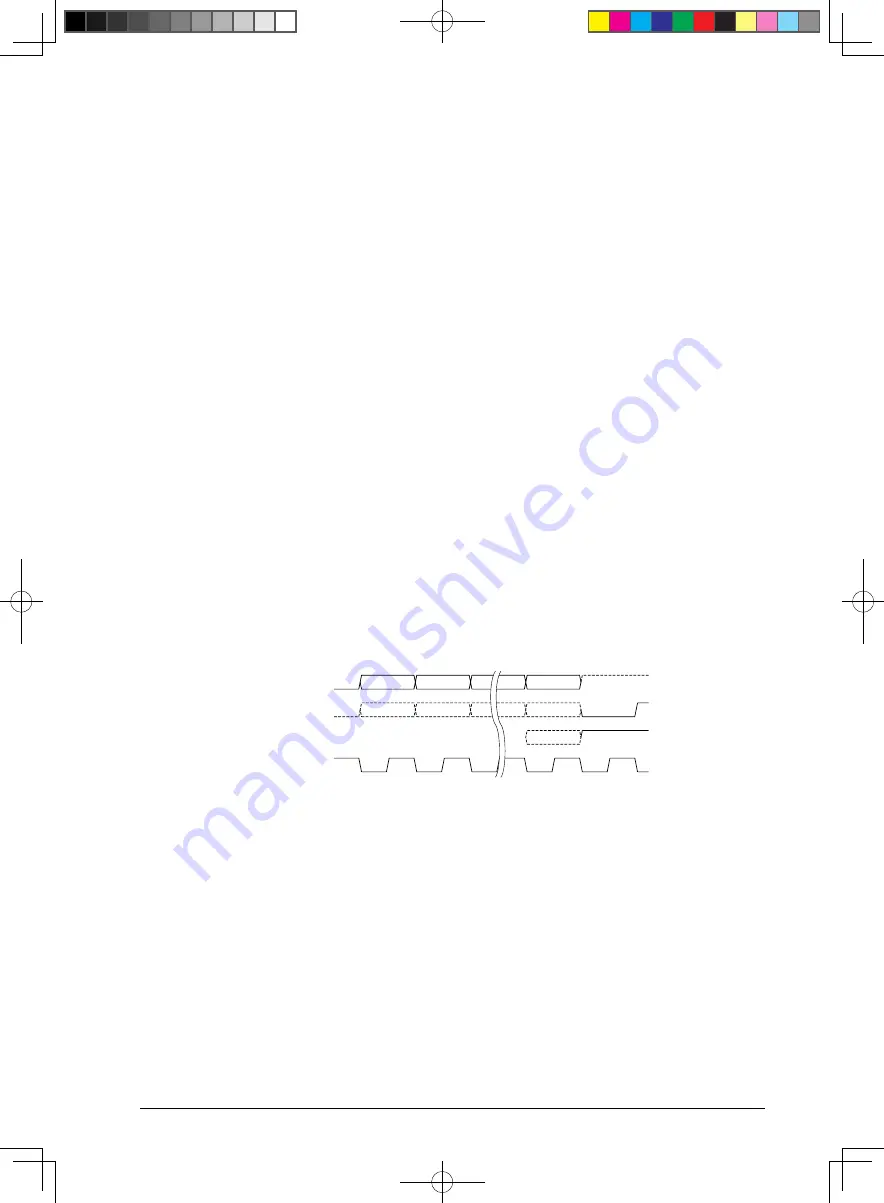

Transmit data bits are output from the SDA1 pin in sync with the SCL1 input clock sent from the master. The

MSB is output first. After the eight bits has been output, the master sends back an ACK or NAK in the ninth

clock cycle.

SDA1 (output)

SDA1 (input)

SCL1 (input)

1

2

8

9

D7

D6

D0

ACK

NAK

5.2 ACK and NAK

Figure 21.

The ACK bit indicates that the master could receive data. It is also a transmit request bit, therefore, the next

transmit data must be written in advance. Receiving an ACK generates a clock stretch status when the clock

stretch function has been enabled, so data can be written after an ACK is received.

A NAK will be returned from the master if the master could not receive data or when the master terminates data

reception. In this case a clock stretch status is not generated even if the clock stretch function has been enabled.

Read DA_NAK/I2CS_STAT register to check if an ACK is returned or if a NAK is returned. DA_NAK is set to

0 when an ACK is returned or set to 1 when a NAK is returned. An interrupt can be generated when DA_NAK

is set to 1, so an error or termination handling can be performed in the interrupt handler routine. DA_NAK is

cleared by writing 1.

The SDA line status during data transmission is input in the module and is compare with the output data. The

comparison results are set to DMS/I2CS_STAT register. DMS is set to 0 when data is output correctly. If the

SDA line status is different from the output data, DMS is set to 1. This may be caused by a low pull-up resistor

value or another device that is controlling the SDA line. An interrupt can be generated when DMS is set to 1, so

an error handling can be performed in the interrupt handler routine. DMS is cleared by writing 1.