Page 38

3. Interrupt Control Circuit

3.2 Interrupt enable register (EIR)

TMP86PM29BUG

Note 1: To clear any one of bits IL7 to IL4, be sure to write "1" into IL2 and IL3.

Note 2: In main program, before manipulating the interrupt enable flag (EF) or the interrupt latch (IL), be sure to clear IMF to "0"

(Disable interrupt by DI instruction). Then set IMF newly again as required after operating on the EF or IL (Enable interrupt

by EI instruction)

In interrupt service routine, because the IMF becomes "0" automatically, clearing IMF need not execute normally on inter-

rupt service routine. However, if using multiple interrupt on interrupt service routine, manipulating EF or IL should be exe-

cuted before setting IMF="1".

Note 3: Do not clear IL with read-modify-write instructions such as bit operations.

Note 1: *: Don’t care

Note 2: Do not set IMF and the interrupt enable flag (EF15 to EF4) to “1” at the same time.

Note 3: In main program, before manipulating the interrupt enable flag (EF) or the interrupt latch (IL), be sure to clear IMF to "0"

(Disable interrupt by DI instruction). Then set IMF newly again as required after operating on the EF or IL (Enable interrupt

by EI instruction)

In interrupt service routine, because the IMF becomes "0" automatically, clearing IMF need not execute normally on inter-

rupt service routine. However, if using multiple interrupt on interrupt service routine, manipulating EF or IL should be exe-

cuted before setting IMF="1".

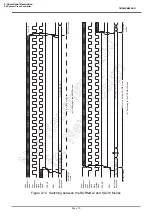

Interrupt Latches

(Initial value: 00000000 000000**)

ILH,ILL

(003DH, 003CH)

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

IL15

IL14

IL13

IL12

IL11

IL10

IL9

IL8

IL7

IL6

IL5

IL4

IL3

IL2

ILH (003DH)

ILL (003CH)

IL15 to IL2

Interrupt latches

at RD

0: No interrupt request

1: Interrupt request

at WR

0: Clears the interrupt request

1: (Interrupt latch is not set.)

R/W

Interrupt Enable Registers

(Initial value: 00000000 0000***0)

EIRH,EIRL

(003BH, 003AH)

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

EF15

EF14

EF13

EF12

EF11

EF10

EF9

EF8

EF7

EF6

EF5

EF4

IMF

EIRH (003BH)

EIRL (003AH)

EF15 to EF4

Individual-interrupt enable flag

(Specified for each bit)

0:

1:

Disables the acceptance of each maskable interrupt.

Enables the acceptance of each maskable interrupt.

R/W

IMF

Interrupt master enable flag

0:

1:

Disables the acceptance of all maskable interrupts

Enables the acceptance of all maskable interrupts

Summary of Contents for TLCS-870/C Series

Page 1: ...8 Bit Microcontroller TLCS 870 C Series TMP86PM29BUG ...

Page 6: ...TMP86PM29BUG ...

Page 7: ...Revision History Date Revision 2007 10 11 1 First Release 2008 8 29 2 Contents Revised ...

Page 9: ......

Page 15: ...vi ...

Page 19: ...Page 4 1 3 Block Diagram TMP86PM29BUG 1 3 Block Diagram Figure 1 2 Block Diagram ...

Page 23: ...Page 8 1 4 Pin Names and Functions TMP86PM29BUG ...

Page 48: ...Page 33 TMP86PM29BUG ...

Page 49: ...Page 34 2 Operational Description 2 3 Reset Circuit TMP86PM29BUG ...

Page 61: ...Page 46 3 Interrupt Control Circuit 3 8 External Interrupts TMP86PM29BUG ...

Page 81: ...Page 66 6 Watchdog Timer WDT 6 3 Address Trap TMP86PM29BUG ...

Page 135: ...Page 120 10 8 Bit TimerCounter TC5 TC6 10 1 Configuration TMP86PM29BUG ...

Page 145: ...Page 130 11 Asynchronous Serial interface UART 11 9 Status Flag TMP86PM29BUG ...

Page 165: ...Page 150 13 10 bit AD Converter ADC 13 6 Precautions about AD Converter TMP86PM29BUG ...

Page 183: ...Page 168 15 LCD Driver 15 4 Control Method of LCD Driver TMP86PM29BUG ...

Page 201: ...Page 186 18 Electrical Characteristics 18 9 Handling Precaution TMP86PM29BUG ...

Page 203: ...Page 188 19 Package Dimensions TMP86PM29BUG ...

Page 205: ......