Page 17

TMP86PM29BUG

Note 1: Always set RETM to “0” when transiting from NORMAL mode to STOP mode. Always set RETM to “1” when transiting

from SLOW mode to STOP mode.

Note 2: When STOP mode is released with

RESET

pin input, a return is made to NORMAL1 regardless of the RETM contents.

Note 3: fc: High-frequency clock [Hz], fs: Low-frequency clock [Hz], *; Don’t care

Note 4: Bits 1 and 0 in SYSCR1 are read as undefined data when a read instruction is executed.

Note 5: As the hardware becomes STOP mode under OUTEN = “0”, input value is fixed to “0”; therefore it may cause external

interrupt request on account of falling edge.

Note 6: When the key-on wakeup is used, RELM should be set to "1".

Note 7: Port P20 is used as

STOP

pin. Therefore, when stop mode is started, OUTEN does not affect to P20, and P20 becomes

High-Z mode.

Note 8: The warmig-up time should be set correctly for using oscillator.

Note 1: A reset is applied if both XEN and XTEN are cleared to “0”, XEN is cleared to “0” when SYSCK = “0”, or XTEN is cleared

to “0” when SYSCK = “1”.

Note 2: *: Don’t care, TG: Timing generator, *; Don’t care

Note 3: Bits 3, 1 and 0 in SYSCR2 are always read as undefined value.

Note 4: Do not set IDLE and TGHALT to “1” simultaneously.

Note 5: Because returning from IDLE0/SLEEP0 to NORMAL1/SLOW1 is executed by the asynchronous internal clock, the period

of IDLE0/SLEEP0 mode might be shorter than the period setting by TBTCR<TBTCK>.

Note 6: When IDLE1/2 or SLEEP1/2 mode is released, IDLE is automatically cleared to “0”.

Note 7: When IDLE0 or SLEEP0 mode is released, TGHALT is automatically cleared to “0”.

Note 8: Before setting TGHALT to “1”, be sure to stop peripherals. If peripherals are not stopped, the interrupt latch of peripherals

may be set after IDLE0 or SLEEP0 mode is released.

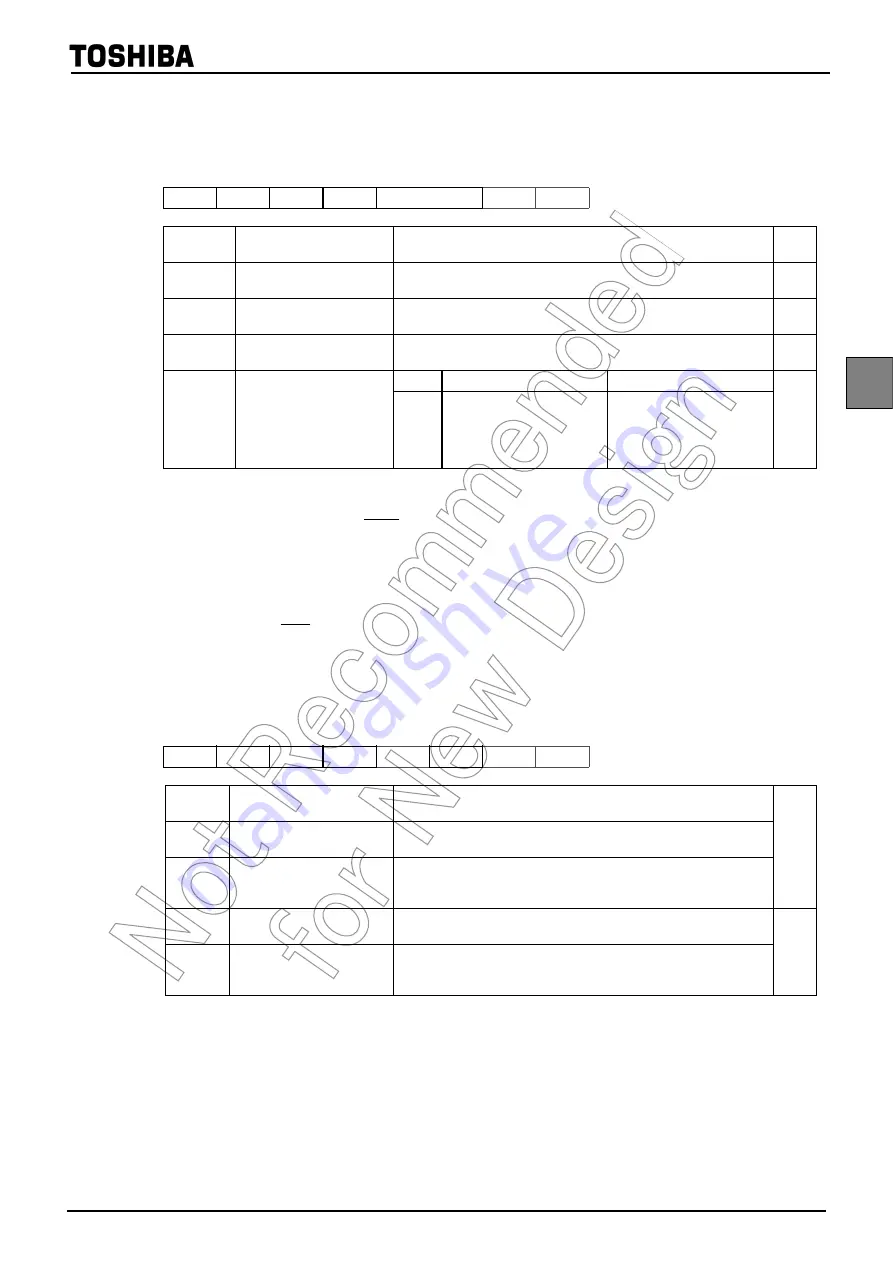

System Control Register 1

SYSCR1

7

6

5

4

3

2

1

0

(0038H)

STOP

RELM

RETM

OUTEN

WUT

(Initial value: 0000 00**)

STOP

STOP mode start

0: CPU core and peripherals remain active

1: CPU core and peripherals are halted (Start STOP mode)

R/W

RELM

Release method for STOP

mode

0: Edge-sensitive release

1: Level-sensitive release

R/W

RETM

Operating mode after STOP

mode

0: Return to NORMAL1/2 mode

1: Return to SLOW1 mode

R/W

OUTEN

Port output during STOP mode

0: High impedance

1: Output kept

R/W

WUT

Warm-up time at releasing

STOP mode

Return to NORMAL mode

Return to SLOW mode

R/W

00

01

10

11

3 x 2

16

/fc

2

16

/fc

3 x 2

14

/fc

2

14

/fc

3 x 2

13

/fs

2

13

/fs

3 x 2

6

/fs

2

6

/fs

System Control Register 2

SYSCR2

(0039H)

7

6

5

4

3

2

1

0

XEN

XTEN

SYSCK

IDLE

TGHALT

(Initial value: 1000 *0**)

XEN

High-frequency oscillator control

0: Turn off oscillation

1: Turn on oscillation

R/W

XTEN

Low-frequency oscillator control

0: Turn off oscillation

1: Turn on oscillation

SYSCK

Main system clock select

(Write)/main system clock moni-

tor (Read)

0: High-frequency clock (NORMAL1/NORMAL2/IDLE1/IDLE2)

1: Low-frequency clock (SLOW1/SLOW2/SLEEP1/SLEEP2)

IDLE

CPU and watchdog timer control

(IDLE1/2 and SLEEP1/2 modes)

0: CPU and watchdog timer remain active

1: CPU and watchdog timer are stopped (Start IDLE1/2 and SLEEP1/2 modes)

R/W

TGHALT

TG control (IDLE0 and SLEEP0

modes)

0: Feeding clock to all peripherals from TG

1: Stop feeding clock to peripherals except TBT from TG.

(Start IDLE0 and SLEEP0 modes)

Summary of Contents for TLCS-870/C Series

Page 1: ...8 Bit Microcontroller TLCS 870 C Series TMP86PM29BUG ...

Page 6: ...TMP86PM29BUG ...

Page 7: ...Revision History Date Revision 2007 10 11 1 First Release 2008 8 29 2 Contents Revised ...

Page 9: ......

Page 15: ...vi ...

Page 19: ...Page 4 1 3 Block Diagram TMP86PM29BUG 1 3 Block Diagram Figure 1 2 Block Diagram ...

Page 23: ...Page 8 1 4 Pin Names and Functions TMP86PM29BUG ...

Page 48: ...Page 33 TMP86PM29BUG ...

Page 49: ...Page 34 2 Operational Description 2 3 Reset Circuit TMP86PM29BUG ...

Page 61: ...Page 46 3 Interrupt Control Circuit 3 8 External Interrupts TMP86PM29BUG ...

Page 81: ...Page 66 6 Watchdog Timer WDT 6 3 Address Trap TMP86PM29BUG ...

Page 135: ...Page 120 10 8 Bit TimerCounter TC5 TC6 10 1 Configuration TMP86PM29BUG ...

Page 145: ...Page 130 11 Asynchronous Serial interface UART 11 9 Status Flag TMP86PM29BUG ...

Page 165: ...Page 150 13 10 bit AD Converter ADC 13 6 Precautions about AD Converter TMP86PM29BUG ...

Page 183: ...Page 168 15 LCD Driver 15 4 Control Method of LCD Driver TMP86PM29BUG ...

Page 201: ...Page 186 18 Electrical Characteristics 18 9 Handling Precaution TMP86PM29BUG ...

Page 203: ...Page 188 19 Package Dimensions TMP86PM29BUG ...

Page 205: ......