Page 35

TMP86PM29BUG

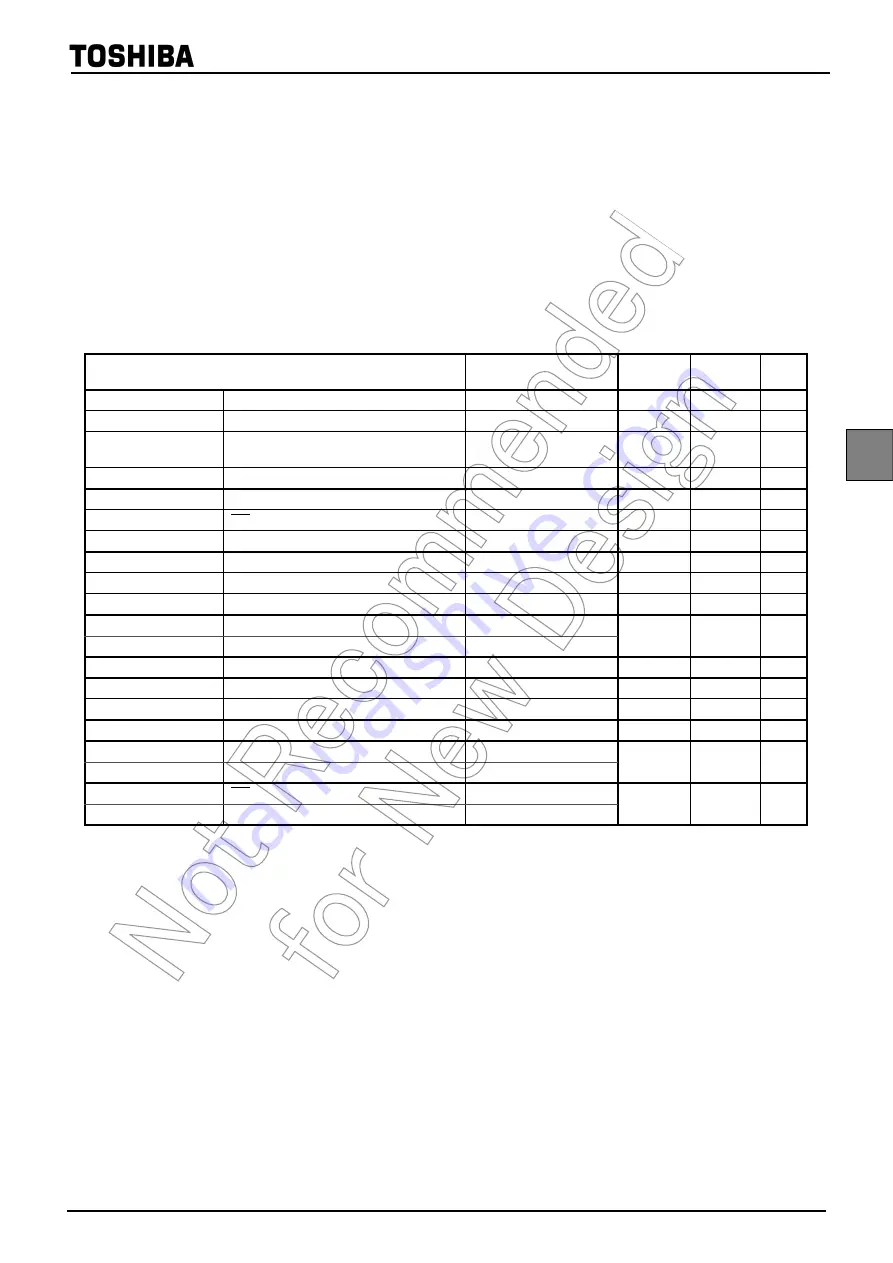

3. Interrupt Control Circuit

The TMP86PM29BUG has a total of 19 interrupt sources excluding reset, of which 3 source levels are multi-

plexed. Interrupts can be nested with priorities. Four of the internal interrupt sources are non-maskable while the rest

are maskable.

Interrupt sources are provided with interrupt latches (IL), which hold interrupt requests, and independent vectors.

The interrupt latch is set to “1” by the generation of its interrupt request which requests the CPU to accept its inter-

rupts. Interrupts are enabled or disabled by software using the interrupt master enable flag (IMF) and interrupt enable

flag (EF). If more than one interrupts are generated simultaneously, interrupts are accepted in order which is domi-

nated by hardware. However, there are no prioritized interrupt factors among non-maskable interrupts.

Note 1: The INTSEL register is used to select the interrupt source to be enabled for each multiplexed source level (see 3.3 Inter-

rupt Source Selector (INTSEL)).

Note 2: To use the address trap interrupt (INTATRAP), clear WDTCR1<ATOUT> to “0” (It is set for the “reset request” after reset is

cancelled). For details, see “Address Trap”.

Note 3: To use the watchdog timer interrupt (INTWDT), clear WDTCR1<WDTOUT> to "0" (It is set for the "Reset request" after

reset is released). For details, see "Watchdog Timer".

3.1

Interrupt latches (IL15 to IL2)

An interrupt latch is provided for each interrupt source, except for a software interrupt and an executed the unde-

fined instruction interrupt. When interrupt request is generated, the latch is set to “1”, and the CPU is requested to

accept the interrupt if its interrupt is enabled. The interrupt latch is cleared to "0" immediately after accepting inter-

rupt. All interrupt latches are initialized to “0” during reset.

The interrupt latches are located on address 003CH and 003DH in SFR area. Each latch can be cleared to "0" indi-

vidually by instruction. However, IL2 and IL3 should not be cleared to "0" by software. For clearing the interrupt

latch, load instruction should be used and then IL2 and IL3 should be set to "1". If the read-modify-write instructions

such as bit manipulation or operation instructions are used, interrupt request would be cleared inadequately if inter-

rupt is requested while such instructions are executed.

Interrupt Factors

Enable Condition

Interrupt

Latch

Vector

Address

Priority

Internal/External

(Reset)

Non-maskable

–

FFFE

1

Internal

INTSWI (Software interrupt)

Non-maskable

–

FFFC

2

Internal

INTUNDEF (Executed the undefined instruction

interrupt)

Non-maskable

–

FFFC

2

Internal

INTATRAP (Address trap interrupt)

Non-maskable

IL2

FFFA

2

Internal

INTWDT (Watchdog timer interrupt)

Non-maskable

IL3

FFF8

2

External

INT0

IMF• EF4 = 1, INT0EN = 1

IL4

FFF6

5

External

INT1

IMF• EF5 = 1

IL5

FFF4

6

Internal

INTTBT

IMF• EF6 = 1

IL6

FFF2

7

External

INT2

IMF• EF7 = 1

IL7

FFF0

8

Internal

INTTC

IMF• EF8 = 1

IL8

FFEE

9

Internal

INTRXD

IMF• EF9 = 1, IL9ER = 0

IL9

FFEC

10

Internal

INTSIO

IMF• EF9 = 1, IL9ER = 1

Internal

INTTXD

IMF• EF10 = 1

IL10

FFEA

11

Internal

INTTC4

IMF• EF11 = 1

IL11

FFE8

12

Internal

INTTC6

IMF• EF12 = 1

IL12

FFE6

13

Internal

INTADC

IMF• EF13 = 1

IL13

FFE4

14

External

INT3

IMF• EF14 = 1, IL14ER = 0

IL14

FFE2

15

Internal

INTTC3

IMF• EF14 = 1, IL14ER = 1

External

INT5

IMF• EF15 = 1, IL15ER = 0

IL15

FFE0

16

Internal

INTTC5

IMF• EF15 = 1, IL15ER = 1

Summary of Contents for TLCS-870/C Series

Page 1: ...8 Bit Microcontroller TLCS 870 C Series TMP86PM29BUG ...

Page 6: ...TMP86PM29BUG ...

Page 7: ...Revision History Date Revision 2007 10 11 1 First Release 2008 8 29 2 Contents Revised ...

Page 9: ......

Page 15: ...vi ...

Page 19: ...Page 4 1 3 Block Diagram TMP86PM29BUG 1 3 Block Diagram Figure 1 2 Block Diagram ...

Page 23: ...Page 8 1 4 Pin Names and Functions TMP86PM29BUG ...

Page 48: ...Page 33 TMP86PM29BUG ...

Page 49: ...Page 34 2 Operational Description 2 3 Reset Circuit TMP86PM29BUG ...

Page 61: ...Page 46 3 Interrupt Control Circuit 3 8 External Interrupts TMP86PM29BUG ...

Page 81: ...Page 66 6 Watchdog Timer WDT 6 3 Address Trap TMP86PM29BUG ...

Page 135: ...Page 120 10 8 Bit TimerCounter TC5 TC6 10 1 Configuration TMP86PM29BUG ...

Page 145: ...Page 130 11 Asynchronous Serial interface UART 11 9 Status Flag TMP86PM29BUG ...

Page 165: ...Page 150 13 10 bit AD Converter ADC 13 6 Precautions about AD Converter TMP86PM29BUG ...

Page 183: ...Page 168 15 LCD Driver 15 4 Control Method of LCD Driver TMP86PM29BUG ...

Page 201: ...Page 186 18 Electrical Characteristics 18 9 Handling Precaution TMP86PM29BUG ...

Page 203: ...Page 188 19 Package Dimensions TMP86PM29BUG ...

Page 205: ......