Semiconductor Group

6-31

1999-04-01

On-Chip Peripheral Components

C541U

This register enables or disables interrupt request for the status bits. SCIEN must only be written

when the SSC interrupts are disabled in the general interrupt enable register IEN2 (9AH) using bit

ESSC otherwise unexpected interrupt requests may occur.

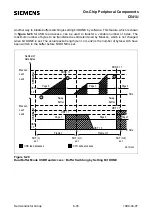

Special Function Register SCIEN (Address ACH)

Reset Value : XXXXXX00B

Note:

The SSC interrupt behaviour is in addition affected by bit ESSC in the interrupt enable

register IEN2 and by bit 2 in the interrupt priority registers IP0 and IP1.

Bit

Function

–

Reserved for future use.

WCEN

SSC write collision interrupt enable

WCEN =0 : No interrupt request will be generated if the WCOL bit in the status

register SCF is set.

WCEN=1 : An interrupt is generated if the WCOL bit in the status register SCF is

set.

TCEN

SSC transfer completed interrupt enable

TCEN =0 : No interrupt request will be generated if the TC bit in the status

register SCF is set.

TCEN=1 : An interrupt is generated if the TC bit in the status register SCF is set.

–

–

–

–

ACH

SCIEN

Bit No.

7

6

5

4

3

2

1

0

MSB

LSB

–

–

WCEN TCEN

Summary of Contents for C541U

Page 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Page 7: ......

Page 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Page 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

Page 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Page 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Page 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...