Semiconductor Group

8-7

1997-10-01

Fail Safe Mechanisms

C541U

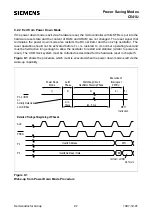

The oscillator watchdog is able to detect a recovery of the on-chip oscillator after a failure. If the

frequency derived from the on-chip oscillator is again higher than the reference the watchdog starts

a final reset sequence which takes typ. 1 ms. Within that time the clock is still supplied by the RC

oscillator and the part is held in reset. This allows a reliable stabilization of the on-chip oscillator.

After that, the watchdog toggles the clock supply back to the on-chip oscillator and releases the

reset request. If no reset is applied in this moment the part will start program execution. If an

external reset is active, however, the device will keep the reset state until also the external reset

request disappears.

Furthermore, the status flag OWDS is set if the oscillator watchdog was active. The status flag can

be evaluated by software to detect that a reset was caused by the oscillator watchdog. The flag

OWDS can be set or cleared by software. An external reset request, however, also resets OWDS

(and WDTS).

8.2.2 Fast Internal Reset after Power-On

The C541U can use the oscillator watchdog unit for a fast internal reset procedure after power-on.

Normally the members of the 8051 family (e. g. SAB 80C52) enter their default reset state not before

the on-chip oscillator starts. The reason is that the external reset signal must be internally

synchronized and processed in order to bring the device into the correct reset state. Especially if a

crystal is used the start up time of the oscillator is relatively long (typ. 1 ms). During this time period

the pins have an undefined state which could have severe effects e.g. to actuators connected to

port pins.

In the C541U the oscillator watchdog unit avoids this situation. After power-on the oscillator

watchdog’s RC oscillator starts working within a very short start-up time (typ. less than 2

microseconds). In the following the watchdog circuitry detects a failure condition for the on-chip

oscillator because this has not yet started (a failure is always recognized if the watchdog’s RC

oscillator runs faster than the on-chip oscillator). As long as this condition is valid the watchdog uses

the RC oscillator output as clock source for the chip. This allows correct resetting of the part and

brings all ports to the defined state. The delay time between power-on and correct reset state is max

34

µ

s. More details about the fast internal reset procedure after power-on are described in chapter

5 of this manual.

Summary of Contents for C541U

Page 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Page 7: ......

Page 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Page 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

Page 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Page 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Page 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...