Semiconductor Group

7-17

1997-10-01

Interrupt System

C541U

7.2

Interrupt Priority Level Structure

A low-priority interrupt can itself be interrupted by a high-priority interrupt, but not by another low-

priority interrupt. A high-priority interrupt cannot be interrupted by any other interrupt source.

If two requests of different priority level are received simultaneously, the request of higher priority is

serviced. If requests of the same priority are received simultaneously, an internal polling sequence

determines which request is serviced. Thus, within each priority level there is a second priority

structure determined by the polling sequence (vertical and horizontal) as shown in table 7-1 below.

If e.g. the external interrupt 0 and the SSC interrupt have the same priority and if they are active

simultaneously, the external interrupt 0 will be serviced first.

Table 7-1

Interrupt Source Structure

Interrupt Source

Priority

External Interrupt 0

Timer 0 Interrupt

External Interrupt 1

Timer 1 Interrupt

SSC Interrupt

USB Endpoint Interrupt

USB Device Interrupt

–

High

Low

High Priority

Low Priority

Summary of Contents for C541U

Page 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Page 7: ......

Page 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Page 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

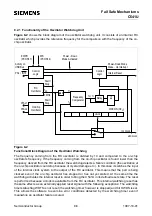

Page 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Page 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Page 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...