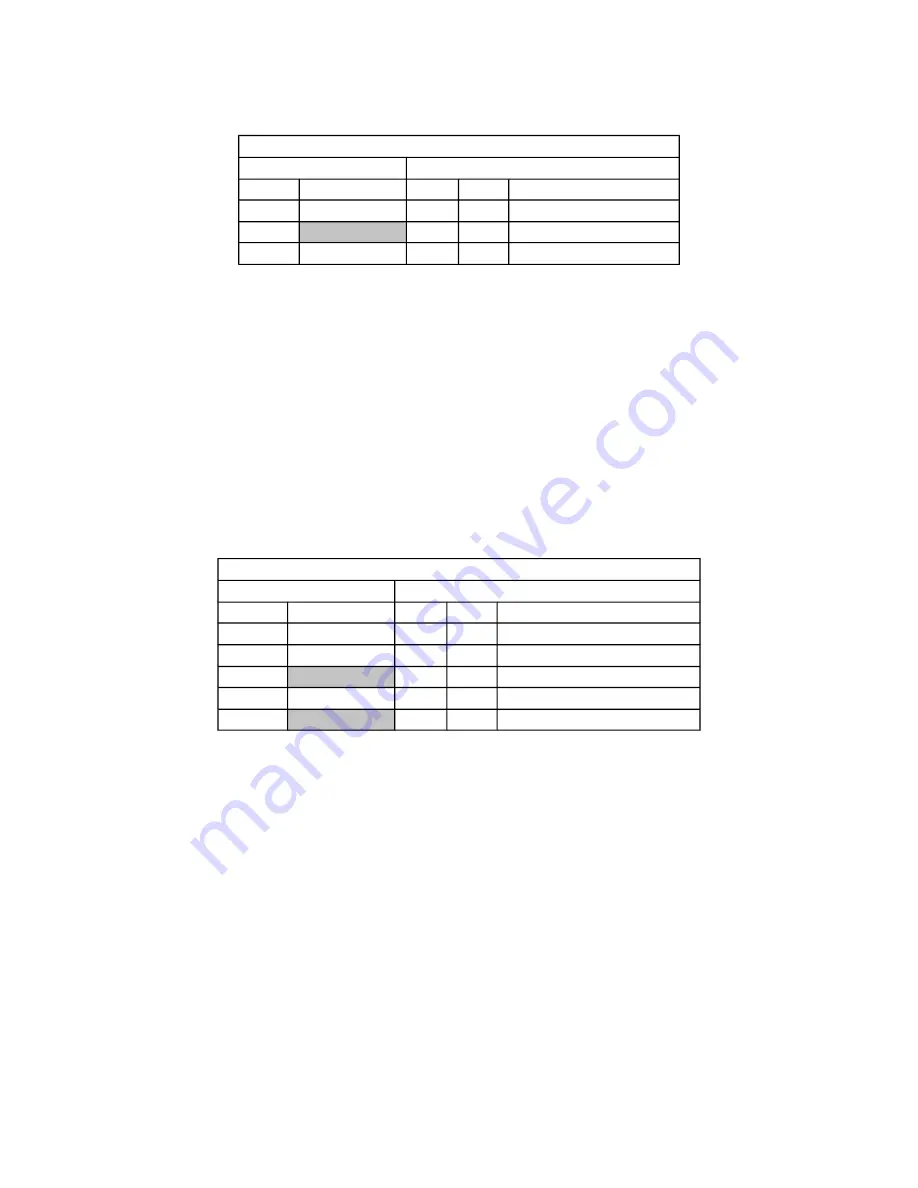

Receive Data Register (

rxdata

)

Register Offset

0x4

Bits

Field Name

Attr.

Rst.

Description

[7:0]

data

RO

X

Received data

[30:8]

Reserved

31

empty

RO

X

Receive FIFO empty

The read-write

txctrl

register controls the operation of the transmit channel. The

txen

bit con-

trols whether the Tx channel is active. When cleared, transmission of Tx FIFO contents is sup-

pressed, and the

txd

pin is driven high.

The

nstop

field specifies the number of stop bits:

0

for one stop bit and

1

for two stop bits.

The

txcnt

field specifies the threshold at which the Tx FIFO watermark interrupt triggers.

The

txctrl

register is reset to

0

.

Transmit Control Register (

txctrl

)

Register Offset

0x8

Bits

Field Name

Attr.

Rst.

Description

0

txen

RW

0x0

Transmit enable

1

nstop

RW

0x0

Number of stop bits

[15:2]

Reserved

[18:16]

txcnt

RW

0x0

Transmit watermark level

[31:19]

Reserved

The read-write

rxctrl

register controls the operation of the receive channel. The

rxen

bit con-

trols whether the Rx channel is active. When cleared, the state of the

rxd

pin is ignored, and no

characters will be enqueued into the Rx FIFO.

The

rxcnt

field specifies the threshold at which the Rx FIFO watermark interrupt triggers.

The

rxctrl

register is reset to

0

. Characters are enqueued when a zero (low) start bit is seen.

Table 57:

Receive Data Register

Table 58:

Transmit Control Register

Copyright © 2019, SiFive Inc. All rights reserved.

81

Содержание FE310-G002

Страница 1: ...SiFive FE310 G002 Manual v19p05 SiFive Inc ...

Страница 11: ...Figure 1 FE310 G002 top level block diagram Copyright 2019 SiFive Inc All rights reserved 9 ...

Страница 15: ...Chapter 2 List of Abbreviations and Terms 13 ...

Страница 23: ...Chapter 4 Memory Map The memory map of the FE310 G002 is shown in Table 4 21 ...