........................................................................................... 58

............................................................................................ 58

............................................................................. 58

................................................................................................. 58

.................................................................................. 61

...................................................................61

....................................................................................... 62

Watchdog Configuration Register (

.............................................................62

...................................................................63

.......................................................................... 63

....................................................................... 64

.......................................................................................... 64

............................................................................... 64

.................................................................65

.................................................................................... 67

Initiate Sleep Sequence Register (

...........................................................68

.................................................................................... 68

...............................69

................................................................................... 71

...................................................71

...................................................................... 72

............................................................................ 72

General Purpose Input/Output Controller (GPIO)

............................74

................................................................................. 76

4

Содержание FE310-G002

Страница 1: ...SiFive FE310 G002 Manual v19p05 SiFive Inc ...

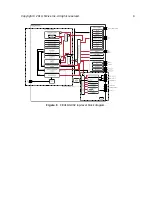

Страница 11: ...Figure 1 FE310 G002 top level block diagram Copyright 2019 SiFive Inc All rights reserved 9 ...

Страница 15: ...Chapter 2 List of Abbreviations and Terms 13 ...

Страница 23: ...Chapter 4 Memory Map The memory map of the FE310 G002 is shown in Table 4 21 ...