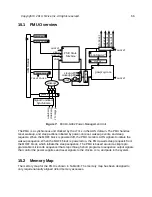

The watchdog timer (WDT) is used to cause a full power-on reset if either hardware or software

errors cause the system to malfunction. The WDT can also be used as a programmable periodic

interrupt source if the watchdog functionality is not required. The WDT is implemented as an

upcounter in the Always-On domain that must be reset at regular intervals before the count

reaches a preset threshold, else it will trigger a full power-on reset. To prevent errant code from

resetting the counter, the WDT registers can only be updated by presenting a WDT key

sequence.

wdogcmp

wdogcf g

wdogcmpi p

wdogcl k

aonr st

wdogcount

wdogs

wdogscal e

>=?

W

d

o

g

T

ile

L

in

k

wdogf eed

r eset

wdogr st

aonr st

en

wdogcl k

wdogkey

cor er st

Synch

wdogzer ocmp

wdogr st en

wdogenal ways

wdogencor eawake

Figure 6:

Watchdog Timer

The WDT is based around a 31-bit counter held in

wdogcount[30:0]

. The counter can be read

or written over the TileLink bus. Bit 31 of

wdogcount

returns a zero when read.

61

Содержание FE310-G002

Страница 1: ...SiFive FE310 G002 Manual v19p05 SiFive Inc ...

Страница 11: ...Figure 1 FE310 G002 top level block diagram Copyright 2019 SiFive Inc All rights reserved 9 ...

Страница 15: ...Chapter 2 List of Abbreviations and Terms 13 ...

Страница 23: ...Chapter 4 Memory Map The memory map of the FE310 G002 is shown in Table 4 21 ...