Copyright © Siemens AG 2010. All rights reserved.

Page

85

ERTEC 400 Manual

Technical data subject to change

Version 1.2.2

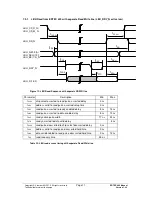

8.1.5

PCI Interrupt Handling:

Interrupt outputs INTA_N, INTB_N, and SERR_N are available at the PCI interface.

An interrupt request from the ARM946 to the PCI bus takes place by write accessing the interrupt controller

integrated in the IRT switch. The interrupts are masked and saved in the IRT switch. This enables operation of a

mailbox from the ARM946 to the PCI host.

An interrupt request from the PCI bus to the ARM946 takes place by write accessing an IRT switch-internal

register. The interrupts are masked and saved in the interrupt controller of the ARM946. This enables operation of

a mailbox from the PCI host to the ARM946.

When PC-based systems are linked, only INTA_N is used (only 1 function of the PCI bridge). The INTB_N output

is not used. When an embedded host processor is linked, both INTA_N and INTB_N can be used. The local ARM

processor is linked via the IRQ0_SP and IRQ1_SP interrupts. Both are linked via the internal logic structure of the

interrupt controller unit (ICU) to the IRQ input of the ARM946E-S. Optionally, the option exists to link these

interrupts to the ARM946E-S by assigning the ICU as FIQ.

Start

(Powerup

Reset)

Primary Boot

(hardware)

Secondary

Boot

(user

specified,

OS Init)

Application

Run

End

Till now, just ARM run, all other AHB

Masters are disabled, so place following

workaround code here:

// fix AHB priority

// Register: M_LOCK_CTRL Address

0x4000264C

M_Clock_Ctrl

|=

0x00000008;